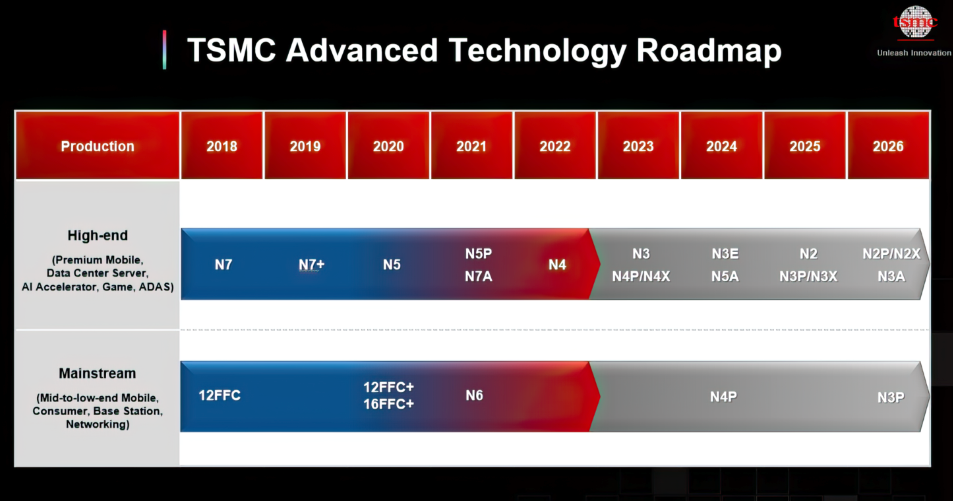

El nodo 3NM de tercera generación de TSMC está en camino, y N3P se producirá en masa más adelante este año

TSMC comenzó con éxito a usar la tecnología de proceso de nivel de 3NM de segunda generación para producir chips en el cuarto trimestre de 2023, logrando el hito planificado.La compañía se está preparando actualmente para producir chips N3P mejorados en masa para este nodo.TSMC anunció en el Simposio de Tecnología Europea que esto tendrá lugar en la segunda mitad de 2024.

El proceso N3E ha ingresado la producción en masa según lo programado, y la densidad de defectos es comparable al proceso N5 durante la producción en masa en 2020. TSMC describe el rendimiento de N3E como "excelente", y actualmente el único procesador que usa N3E - Apple M4- tiene significativamenteaumentó el número de transistores y la velocidad del reloj operativo en comparación con M3 en función de la tecnología N3.

Un ejecutivo de TSMC dijo en el evento: "N3E comenzó la producción en masa según lo planeado en el cuarto trimestre del año pasado. Hemos visto un excelente rendimiento de producción de los productos de nuestros clientes, por lo que de hecho han ingresado al mercado según lo planeado".

Un ejecutivo de TSMC dijo en el evento: "N3E comenzó la producción en masa según lo planeado en el cuarto trimestre del año pasado. Hemos visto un excelente rendimiento de producción de los productos de nuestros clientes, por lo que de hecho han ingresado al mercado según lo planeado".

El detalle clave del proceso N3E es su simplificación en comparación con el proceso N3 de primera generación de TSMC (también conocido como N3B).Al eliminar algunas capas que requieren litografía EUV y evitar completamente el uso de patrón doble EUV, N3E reduce los costos de producción, amplía la ventana del proceso y mejora el rendimiento.Sin embargo, estos cambios a veces reducen la densidad del transistor y la eficiencia energética, una compensación que se puede mitigar a través de la optimización del diseño.

Mirando hacia el futuro, el proceso N3P proporciona escala óptica para N3E y también muestra un progreso prometedor.Ha aprobado la certificación de calificación necesaria y muestra un rendimiento de rendimiento cerca de N3E.La próxima evolución de la cartera de tecnología de TSMC tiene como objetivo mejorar el rendimiento hasta en hasta un 4% o reducir el consumo de energía en aproximadamente un 9% a la misma velocidad del reloj, al tiempo que aumenta la densidad del transistor de los chips de configuración de diseño híbrido en un 4%.

N3p mantiene la compatibilidad con los módulos IP de N3E, las herramientas de diseño y los métodos, lo que lo convierte en una opción atractiva para los desarrolladores.Esta continuidad garantiza que se espera que la mayoría de los diseños de chips nuevos (chips) pasen de usar N3E a N3P, aprovechando el rendimiento mejorado y la eficiencia de costos de este último.

Se espera que el trabajo final de preparación de producción para N3P tenga lugar en la segunda mitad de este año, cuando ingresará a la etapa de HVM (producción en masa).TSMC espera que los diseñadores de chips lo adopten de inmediato.Dado su rendimiento y ventajas de costos, se espera que N3P sea favorecido por los clientes de TSMC, incluidos Apple y AMD.

Aunque la fecha de lanzamiento exacta de los chips basados en N3P aún es incierta, se espera que los principales fabricantes como Apple usen esta tecnología en su serie de procesadores para 2025, incluido SOC para teléfonos inteligentes, computadoras personales y tabletas.

"También hemos entregado con éxito la tecnología N3P", dijeron los ejecutivos de TSMC."Ha sido certificado y su rendimiento de rendimiento es cercano a N3E. (Tecnología de procesos) también ha recibido obleas de clientes y la producción comenzará en la segunda mitad de este año. Debido a N3P (PPA Advantage), esperamos que la mayoría de losLas obleas en N3 fluyen hacia N3P ".

Mirando hacia el futuro, el proceso N3P proporciona escala óptica para N3E y también muestra un progreso prometedor.Ha aprobado la certificación de calificación necesaria y muestra un rendimiento de rendimiento cerca de N3E.La próxima evolución de la cartera de tecnología de TSMC tiene como objetivo mejorar el rendimiento hasta en hasta un 4% o reducir el consumo de energía en aproximadamente un 9% a la misma velocidad del reloj, al tiempo que aumenta la densidad del transistor de los chips de configuración de diseño híbrido en un 4%.

N3p mantiene la compatibilidad con los módulos IP de N3E, las herramientas de diseño y los métodos, lo que lo convierte en una opción atractiva para los desarrolladores.Esta continuidad garantiza que se espera que la mayoría de los diseños de chips nuevos (chips) pasen de usar N3E a N3P, aprovechando el rendimiento mejorado y la eficiencia de costos de este último.

Se espera que el trabajo final de preparación de producción para N3P tenga lugar en la segunda mitad de este año, cuando ingresará a la etapa de HVM (producción en masa).TSMC espera que los diseñadores de chips lo adopten de inmediato.Dado su rendimiento y ventajas de costos, se espera que N3P sea favorecido por los clientes de TSMC, incluidos Apple y AMD.

Aunque la fecha de lanzamiento exacta de los chips basados en N3P aún es incierta, se espera que los principales fabricantes como Apple usen esta tecnología en su serie de procesadores para 2025, incluido SOC para teléfonos inteligentes, computadoras personales y tabletas.

"También hemos entregado con éxito la tecnología N3P", dijeron los ejecutivos de TSMC."Ha sido certificado y su rendimiento de rendimiento es cercano a N3E. (Tecnología de procesos) también ha recibido obleas de clientes y la producción comenzará en la segunda mitad de este año. Debido a N3P (PPA Advantage), esperamos que la mayoría de losLas obleas en N3 fluyen hacia N3P ".