SPI desmitificó la exploración de los fundamentos de la interfaz periférica en serie

El protocolo de interfaz periférica en serie (SPI) emerge como una piedra angular en el ámbito de la comunicación digital, especialmente en sistemas integrados que requieren intercambios de datos robustos de alta velocidad.Originalmente desarrollado para facilitar el flujo de datos sin problemas entre los microcontroladores y los dispositivos periféricos, SPI se distingue con sus capacidades síncronas y dúplex, garantizando la comunicación bidireccional simultánea.Este protocolo emplea una arquitectura maestra-esclavo, utilizando cuatro líneas principales: maestro, esclavo en (Mosi);Maestro en, esclavo (miso);Reloj (sck);y Slave Select (SS): establecer un entorno controlado y eficiente para la transmisión de datos.Al admitir una variedad de modos y configuraciones operativas, incluidas configuraciones de 3 hilos y múltiples IO, SPI se adapta a diversas demandas tecnológicas, que respaldan su extensa aplicación en varios sectores, como la electrónica automotriz, los sistemas de control industrial y la electrónica de consumo.Esta exploración en profundidad profundiza en las complejidades técnicas de SPI, discutiendo sus configuraciones, tipos de transacciones y programación, junto con su papel clave en los diseños y sistemas electrónicos modernos.

Catalogar

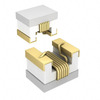

Figura 1: bus de interfaz periférica en serie (SPI)

Las capacidades y características de SPI

El bus de interfaz periférica en serie (SPI) es clave para la transferencia de datos sincrónicas rápida, completa y dúplex entre un dispositivo maestro y múltiples dispositivos de esclavos.A diferencia de otros protocolos, SPI utiliza cuatro líneas de datos principales: Master Out, Slave in (Mosi), Master in, Slave Out (Miso), Clock (SCK) y Slave Select (SS).Esta configuración permite un manejo de datos eficiente y robusto para varias aplicaciones.

Figura 2: Configuración del esclavo maestro

En un sistema SPI, los datos fluyen simultáneamente en ambas direcciones, lo que permite la comunicación en tiempo real.El maestro envía datos al esclavo a través de la línea MOSI y recibe datos del esclavo a través de la línea de miso al mismo tiempo.Los dispositivos SPI pueden transmitir datos que comienzan con el bit más significativo (MSB) o el bit menos significativo (LSB).Esto requiere una configuración cuidadosa de acuerdo con la hoja de datos del dispositivo para garantizar la secuencia de bits correcta.Por ejemplo, en los proyectos de Arduino, se necesitan directrices detalladas de configuración del puerto SPI para que coincidan con los requisitos del dispositivo específico, como se describe en las referencias técnicas y las hojas de datos.

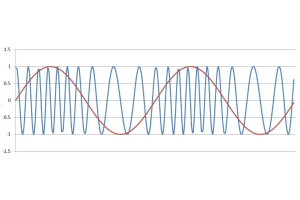

Figura 3: Polaridad y fase del reloj

La precisión de la transferencia de datos en SPI depende de configurar correctamente la polaridad del reloj (CPOL) y la fase (CPHA), que determinan cómo los bits de datos se alinean y se capturan durante la comunicación.SPI admite cuatro modos para acomodar diferentes necesidades de tiempo:

• Modo 0 (CPOL = 0, CPHA = 0)

El reloj es inactivo bajo.Los bits de datos se capturan en el borde ascendente del reloj y se transmiten en el borde que cae.Los datos deben estar listos antes del primer pulso de reloj ascendente.

• Modo 1 (CPOL = 0, CPHA = 1)

El reloj es inactivo bajo.Los bits de datos se capturan en el borde que cae y se transmiten en el siguiente borde ascendente.

• Modo 2 (CPOL = 1, CPHA = 0)

El reloj está inactivo.Los datos se capturan en el borde que cae y se transmite en el borde ascendente.Los datos deben estar listos antes del primer pulso de reloj que cae.

• Modo 3 (CPOL = 1, CPHA = 1)

El reloj está inactivo.Los bits de datos se capturan en el borde ascendente y se transmiten en el borde que cae.

Cada modo garantiza la integridad de los datos alineando con precisión los bits de datos con las transiciones de reloj, evitando la corrupción de datos y garantizando intercambios confiables entre los dispositivos maestros y esclavos.

Glosario de términos clave

Para comprender el protocolo SPI, se requiere conocer los siguientes términos clave que definen las interacciones del dispositivo:

CLK (reloj en serie): esta es la señal de sincronización, controlada por el dispositivo maestro, que determina cuándo los bits de datos se muestrean y cambian durante la comunicación.Establece el ritmo para la transmisión de datos a través del bus SPI.

SSN (Slave Select): esta señal de control activa baja, administrada por el maestro, selecciona el dispositivo esclavo activo para la comunicación.Cuando esta señal es baja, indica que el dispositivo esclavo está listo para recibir datos o enviar datos al maestro.

MOSI (Master Out, Slave In): este canal de datos envía información del maestro al esclavo.Los datos fluyen a través de esta línea de acuerdo con las señales del reloj, asegurando que los bits se transmitan secuencialmente desde el maestro a uno o más esclavos.

MISO (maestro en, esclavo): esta es la ruta de datos para enviar información del esclavo al maestro.Complementa la línea MOSI, permitiendo un intercambio de datos de dos vías dentro del marco SPI.

CPOL (Polaridad del reloj): esta configuración determina si la línea del reloj es alta o baja cuando no se produce transmisión de datos.Afecta la estabilidad del estado inactivo y la preparación para la siguiente transmisión de datos.

CPHA (fase de reloj): esto especifica cuándo se deben muestrear los datos, ya sea en el borde del reloj al comienzo del ciclo o en el borde que ocurre en la mitad del ciclo.Es clave para alinear con precisión los bits de datos con los pulsos de reloj.

Dominar la conectividad con los métodos de la cadena Slave Select y Daisy

Figura 4: Configuración de selección de múltiples esclavos

Cuando un dispositivo SPI maestro se comunica con múltiples esclavos, cada esclavo tiene su propia línea de selección de esclavos (SS).Esta configuración evita las colisiones de datos y garantiza que los comandos o datos enviados por el maestro alcance solo el esclavo previsto.Solo una línea SS debe estar activa a la vez para evitar conflictos en el maestro en la línea esclava (miso), que podría corromper datos.Si no es necesaria la comunicación de devolución de los esclavos, el maestro puede activar múltiples líneas SS para transmitir comandos o datos a varios esclavos simultáneamente.

Para los sistemas que necesitan más dispositivos de esclavos que los pines de E/S disponibles en el maestro, se usa la expansión de E/S usando hardware como un decodificador o demultiplexor (por ejemplo, el 74HC (t) 238).Esto permite que un solo maestro administre muchos esclavos de manera eficiente al decodificar algunas líneas de control en múltiples líneas SS.

Figura 5: Configuración de la cadena de margaritas

Configuración de la cadena de margaritas

La topología de la cadena Daisy conecta múltiples dispositivos de esclavos en serie, utilizando una sola línea SS.El maestro envía datos al primer esclavo, que lo procesa y los pasa al siguiente esclavo.Esto continúa hasta el último esclavo, que puede enviar datos al maestro a través de la línea MISO.Esta configuración simplifica el cableado y es útil en aplicaciones como matrices LED controladas secuencialmente, donde cada dispositivo necesita datos pasados a través de sus predecesores.

Este método requiere tiempo y manejo de datos precisos para garantizar que cada esclavo interprete correctamente y reenvíe datos.El SPI Master debe administrar meticulosamente el reloj y el flujo de datos para acomodar retrasos de propagación y tiempos de configuración para cada esclavo de la cadena.

Estrategias para una programación efectiva en SPI

La programación para SPI implica conectar microcontroladores con periféricos SPI incorporados para habilitar la transferencia de datos de alta velocidad.Para los usuarios de Arduino, hay dos formas principales de implementar la comunicación SPI:

Usando comandos de cambio

El primer método utiliza los comandos ShiftIn () y ShiftOut ().Estos comandos basados en software permiten flexibilidad para elegir pines y se pueden usar en cualquier alfiler de E/S digital.Esta versatilidad es útil para varias configuraciones de hardware.Sin embargo, debido a que este método se basa en el software para manejar la manipulación y el tiempo de bits, funciona a una velocidad más baja en comparación con el SPI basado en hardware.

Utilizando la biblioteca SPI

El segundo método es más eficiente e implica usar la biblioteca SPI, que accede directamente al hardware SPI a bordo de Arduino.Esto da como resultado tipos de cambio de datos mucho más rápidos.Sin embargo, este método restringe el uso de pines específicos designados por SPI definidos por la arquitectura del microcontrolador.

Al programar la comunicación SPI, es significativo seguir las especificaciones del dispositivo conectado desde su hoja de datos.Esto incluye establecer el orden de bits correcto (MSB o LSB primero) y configurar con precisión la fase de reloj (CPHA) y Polarity (CPOL).La biblioteca SPI en Arduino proporciona funciones como setBitorder (), setDatamode () y setClockDivider () para ajustar estos parámetros, asegurando interacciones suaves y compatibles con varios dispositivos SPI.

Para los tableros Arduino, la gestión del pin Select (CS) de chips es imprescindible.Los tableros más antiguos, como el Arduino Uno, requieren un control manual de este PIN para comenzar y terminar las sesiones de comunicación.En la diferencia, modelos más nuevos como el Arduino debido ofrecen control automático de CS, lo que hace que las operaciones SPI sean más fáciles y confiables.

Configuración del bus SPI: configuraciones de 3 hilos y múltiples IO

El protocolo SPI se adapta a diversas necesidades operativas a través de diferentes configuraciones, incluida la configuración estándar de 4 hilos, así como formatos especializados como modos de 3 hilos y múltiples II.

Figura 6: configuración de 3 hilos

Configuración de 3 hilos

El modo de 3 hilos combina el maestro, esclavo en (MOSI) y maestro en las líneas de esclavo (miso) en una sola línea de datos bidireccional.Esto reduce el número total de pines requeridos a tres: la línea de datos combinadas, la línea de reloj (CLK) y la línea de selección de esclavos (SS).Operando en modo medio-dúplex, esta configuración puede enviar o recibir datos en un momento dado, pero no ambos simultáneamente.Si bien reducir el recuento de pin es beneficioso para dispositivos con disponibilidad limitada de GPIO, esta configuración también limita el rendimiento de los datos.Es adecuado para aplicaciones donde la conservación del espacio y la simplicidad del hardware son prioridades, y la transmisión de datos de alta velocidad es menos riesgosa.

Figura 7: Configuraciones multi-IO

Configuraciones múltiples

Las configuraciones múltiples de IO, incluidos los modos de E/S de doble y quad, expanden las líneas de datos más allá de la línea única que se ve en SPI tradicional.Estos modos usan dos o cuatro líneas para la transmisión de datos, lo que permite tasas de datos mucho más rápidas al habilitar el flujo de datos bidireccional simultáneo.Esta capacidad es especialmente ventajosa en entornos de alto rendimiento donde la velocidad se está asentando.

I/o: Utiliza dos líneas de datos, duplicando efectivamente la velocidad de transferencia de datos en comparación con la configuración de línea de una sola línea.

Quad I/O: Emplea cuatro líneas de datos, aumentando significativamente el rendimiento y la eficiencia.Este modo es particularmente efectivo para las operaciones de ejecución en el lugar (XIP) directamente desde dispositivos de memoria no volátiles como el almacenamiento flash, donde los datos se pueden transmitir en las cuatro líneas simultáneamente.

Estos modos de E/S mejorados corren la brecha entre las interfaces paralelas tradicionales, que generalmente requieren más alfileres para Tasas de datos comparables y configuraciones en serie más eficientes en PIN.Al aumentar el Número de líneas de datos, las configuraciones multi-io aumentan el rendimiento mientras mantener un equilibrio entre el recuento de pines y la eficiencia operativa, haciéndolos Adecuado para una amplia gama de aplicaciones de datos de alta velocidad.

Ejecución de una transacción de escritura SPI simple

La ejecución de una transacción de escritura a la memoria flash SPI implica secuencias de comando precisas para garantizar la integridad de los datos y la comunicación efectiva entre el maestro y el dispositivo esclavo.La operación comienza con el maestro que activa la línea de selección de esclavos (SS), lo que indica que el dispositivo de esclavos de destino comience una sesión de comunicación.Este paso es núcleo, ya que prepara el dispositivo esclavo específico para recibir datos.

Después de activar la línea SS, el maestro envía un comando de escritura junto con los bytes de datos requeridos.Este comando típicamente especifica la acción que se realizará, como 'Registro de estado de escritura', seguido de los bytes de datos que definen el nuevo contenido del registro.La precisión en este paso es dinámica;Cualquier error en el comando o datos puede conducir a configuraciones incorrectas o corrupción de datos.Durante esta fase, la línea de miso permanece en un estado de alta impedancia para evitar que cualquier dato se envíe de regreso al maestro.Esta configuración simplifica la transacción, centrándose únicamente en enviar datos al esclavo.

Una vez que se completa la transmisión de datos, el maestro desactiva la línea SS, marcando el final de la transacción.Esta desactivación le dice al dispositivo de esclavos que la sesión de comunicación ha terminado, lo que le permite regresar a la espera y procesar los datos recibidos.

¿Cómo realizar una transacción SPI Read?

Realizar una transacción de lectura de la memoria flash SPI implica un proceso paso a paso para extraer con precisión los datos del dispositivo de esclavos.Esta operación requiere enviar una instrucción de lectura específica al esclavo, seguido de la recuperación de datos secuenciales.El proceso comienza con el maestro activando la línea Slave Select (SS).Esto aísla y se dirige al dispositivo de esclavos específico para la comunicación, asegurando que los comandos se dirigan exclusivamente al esclavo previsto.

Paso 1: Enviar la instrucción de lectura

Una vez que se selecciona el esclavo, el maestro envía una instrucción de lectura.Este comando inicia la transferencia de datos del esclavo al maestro.La precisión en este comando es clave para garantizar que el esclavo comprenda qué datos se solicitan.

Paso 2: Recuperación de datos

Después de enviar la instrucción, el esclavo comienza a transmitir los datos solicitados al maestro a través del maestro en la línea de esclavo (miso).Esta transmisión de datos ocurre en varios ciclos de reloj, controlados por el reloj del maestro.El maestro lee los bytes de datos secuencialmente, generalmente involucrando un número predefinido de bytes basados en los requisitos del comando.

Figura 8: Transacción Quad IO SPI

Mejora de la transferencia de datos con transacciones Quad IO SPI

El modo Quad IO SPI mejora la comunicación de memoria flash mediante el uso de cuatro líneas de datos bidireccionales.Esta configuración aumenta significativamente las tasas de transferencia de datos en comparación con las configuraciones SPI de una sola o dually.

Desglose detallado del modo Quad IO

La transacción comienza cuando el dispositivo maestro envía un comando 'lectura rápida'.Este comando está específicamente optimizado para acelerar el proceso de lectura, que es necesario para aplicaciones que requieren un acceso rápido a grandes cantidades de datos, como en la computación de alto rendimiento y los sistemas incrustados avanzados.

Después de que se envía el comando, el maestro transmite una dirección de 24 bits.Esta dirección identifica la ubicación exacta en la memoria flash desde la cual se deben leer los datos.Después de la dirección, se envían 8 bits de modo.Estos bits de modo configuran los parámetros de lectura del dispositivo esclavo, ajustando la operación para satisfacer las necesidades de rendimiento específicas.

Una vez que se establecen el comando y los parámetros, el dispositivo esclavo comienza a transmitir datos al maestro.Los datos se envían en unidades de 4 bits (mordisques) a través de las cuatro líneas, cuadruplando efectivamente el rendimiento en comparación con los modos SPI estándar.

Ventajas del modo Quad IO

El uso de cuatro líneas de E/S en el modo Quad IO no solo aumenta las velocidades de transferencia de datos, sino que también mejora la eficiencia general y el rendimiento de la interfaz.Esta configuración reduce significativamente el tiempo necesario para el acceso y la ejecución de datos, lo que lo hace perfecto para operaciones avanzadas de memoria flash.

Utilizando el ejercicio SPI para las transacciones Quad IO

La herramienta SPI Ejecutor es invaluable para administrar estas transacciones complejas.Admite un lenguaje de comando robusto, que permite transiciones suaves entre diferentes modos operativos, como cambiar de una configuración estándar de 4 hilos al modo Quad IO, dentro de una sola transacción.Esta flexibilidad facilita las pruebas y la depuración eficientes de las configuraciones SPI, asegurando que los sistemas puedan aprovechar completamente las capacidades de la tecnología Quad IO.

Descripción general de las transacciones de autobuses SPI

El protocolo de bus SPI (interfaz periférica en serie), aunque no está estandarizado en su estructura de flujo de datos, utiliza comúnmente un formato de facto que garantiza la compatibilidad e interoperabilidad entre los dispositivos de diferentes fabricantes.Esta flexibilidad hace que SPI sea una opción versátil para varias aplicaciones, desde una simple recopilación de datos del sensor hasta tareas complejas de memoria y comunicación.

Formato de transacción común

La mayoría de los dispositivos SPI siguen un patrón general en sus procesos de intercambio de datos, que generalmente involucran estos pasos:

• Fase de comando

El dispositivo maestro inicia la transacción enviando un comando.Este comando especifica el tipo de operación que se realizará, como leer o escribir en el dispositivo esclavo.

• Fase de dirección

Para operaciones que involucran ubicaciones o registros de memoria específicos, el maestro envía una dirección.Esta dirección le dice al esclavo exactamente dónde leer o escribir.

• Fase de datos

Dependiendo del comando, los datos se envían desde el maestro al esclavo o viceversa.En las operaciones de escritura, el maestro envía datos para almacenarse en la ubicación especificada en el dispositivo de esclavos.En las operaciones de lectura, el esclavo envía los datos solicitados al maestro.

Versatilidad de la aplicación

Integración del sensor: la capacidad de SPI para manejar ráfagas cortas de datos de alta velocidad lo hace ideal para sensores que necesitan actualizaciones de datos rápidos, como las de los sistemas de seguridad automotriz.

Acceso a la memoria: SPI se usa ampliamente en operaciones de memoria flash, administrando eficientemente la transmisión de datos hacia y desde chips de memoria, especialmente en sistemas donde el rendimiento y la velocidad son riesgosos.

Módulos de comunicación: los dispositivos como módems y adaptadores de red usan SPI para la transmisión de datos confiable, aprovechando su velocidad y eficiencia para garantizar una comunicación sin problemas.

Explorando las ventajas de SPI: ¿Por qué importa?

El protocolo de interfaz periférica en serie (SPI) ofrece varios beneficios clave que lo convierten en una opción preferida para una variedad de aplicaciones electrónicas.Estos incluyen transferencia de datos de alta velocidad, requisitos de hardware simples y gestión eficiente de múltiples periféricos.

|

Ventajas de SPI

|

|

|

Altas tasas de transferencia de datos |

SPI admite una transferencia de datos mucho más alta Tasas que las comunicaciones en serie asincrónicas estándar.Esta alta velocidad Se requiere capacidad para aplicaciones que necesitan actualizaciones de datos rápidos o Procesamiento en tiempo real, como transmisión de dispositivos de audio y video, de alta velocidad sistemas de adquisición de datos y comunicación entre microcontroladores y Los periféricos como los sensores y los módulos de memoria.

|

|

Hardware simple |

Recibir datos a través de SPI requiere mínimo Hardware, generalmente solo un simple registro de turno.Esta simplicidad se reduce complejidad y costo, lo que hace que SPI sea ideal para sistemas con espacio y presupuesto restricciones.Los registros de cambio facilitan la transferencia directa de datos dentro y fuera de registros digitales estándar, aliviando la integración de SPI en sistemas digitales. |

|

Gestión eficiente de múltiples Periféricos |

SPI es altamente eficiente en el manejo múltiples dispositivos periféricos.A diferencia de otros protocolos que necesitan bus complejos Gestión o señalización adicional Para cada dispositivo, SPI utiliza la selección de esclavos (SS) Línea para administrar múltiples dispositivos.Cada dispositivo de esclavos en el bus SPI puede ser dirigido individualmente a través de su propia línea SS, permitiendo una fácil expansión para incluir más periféricos sin cambios significativos en el núcleo Protocolo de comunicación. |

|

Versatilidad en todas las aplicaciones |

La versatilidad de SPI es evidente en su Adopción generalizada en varios campos.De sistemas integrados en Aplicaciones automotrices e industriales a la electrónica de consumo y telecomunicaciones, SPI proporciona un método confiable y eficiente de comunicación de corta distancia entre un controlador central y su periféricos.Su capacidad para operar a diferentes frecuencias de reloj y Las configuraciones (como los números variables de líneas de datos) mejoran aún más adaptabilidad a requisitos específicos del proyecto.

|

Los desafíos y desventajas del uso de SPI

Si bien el protocolo de interfaz periférica en serie (SPI) ofrece numerosas ventajas, también tiene ciertas limitaciones que pueden afectar su idoneidad para aplicaciones específicas.Teniendo en cuenta estas desventajas es significativa para diseñar sistemas y elegir el protocolo de comunicación correcto.

|

Desventajas de SPI |

|

|

Aumento de los requisitos de la línea de señal |

SPI requiere más líneas de señal que Métodos de comunicación más simples como I²C o UART.Una típica configuración de SPI necesita en Mínimo cuatro líneas: Clock (CLK), Master Out Slave in (Mosi), maestro en esclavo Out (miso) y esclavo select (ss).Esta necesidad de múltiples líneas aumenta Complejidad de cableado, especialmente en sistemas con muchos periféricos.Esto puede liderar a problemas con la integridad de la señal y las restricciones de diseño físico.

|

|

Protocolo de comunicación predefinido |

SPI requiere un bien definido y Protocolo de comunicación estructurado antes de la implementación.No es compatible transmisión de datos ad-hoc o sobre la marcha, lo que limita la flexibilidad en la dinámica sistemas donde las necesidades de comunicación pueden cambiar después de la implementación.Cada La transacción debe ser iniciada y controlada explícitamente por el dispositivo maestro, con comandos y respuestas predefinidos, lo que puede complicar el software Escalabilidad de gastos generales y del sistema.

|

|

Comunicación controlada por maestría |

En una configuración SPI, el dispositivo maestro controla todas las comunicaciones, sin apoyo nativo para igual a igual Comunicación entre dispositivos de esclavos.Este control centralizado puede causar ineficiencias y cuellos de botella, especialmente en sistemas complejos donde múltiples Los dispositivos deben interactuar de forma independiente sin involucrar al maestro.

|

|

Gestión de múltiples líneas SS |

Manejo de múltiples líneas de selección de esclavos (SS) se vuelve engorroso a medida que aumenta el número de periféricos.Cada dispositivo de esclavos en el bus SPI requiere una línea SS única controlada por el maestro, complicando el GPIO del dispositivo maestro (entrada/salida de uso general) configuración y software.Administrar estas líneas de manera efectiva, particularmente Al escalar el sistema para incluir más dispositivos, puede aumentar el diseño y sobrecarga operativa. |

Aplicaciones de la interfaz periférica en serie (SPI) en tecnología

La flexibilidad de SPI y las altas tasas de transferencia de datos lo hacen ideal para diversas aplicaciones en todas las industrias, desde redes de sensores hasta electrónica automotriz.Aquí hay una mirada más cercana a cómo se usa SPI en diferentes sectores:

Figura 9: Redes de sensores

SPI se está instalando en redes de sensores, especialmente en entornos intensivos en datos como las estaciones meteorológicas.Permite un intercambio de datos rápido y eficiente entre microcontroladores y sensores que monitorean la temperatura, la humedad y la presión atmosférica, lo que permite la recopilación y el procesamiento de datos en tiempo real.

Figura 10: Dispositivos de memoria

En el almacenamiento de memoria, SPI se usa ampliamente con chips de memoria flash y Eeproms.Admite lecturas y escrituras de datos de alta velocidad, lo que permite a los sistemas integrados realizar operaciones de almacenamiento de datos eficientes, lo cual es dinámico para aplicaciones que requieren actualizaciones o recuperación de datos frecuentes.

Figura 11: módulos de visualización

Las tecnologías de visualización como LCD y paneles OLED usan SPI para recibir datos de un microcontrolador.Esto permite la actualización dinámica del contenido de pantalla, que es necesario para dispositivos que requieren interacción del usuario y retroalimentación visual, como relojes digitales, reproductores de MP3 y dispositivos portátiles inteligentes.

Figura 12: Módulos de comunicación

SPI mejora los módulos de comunicación como los transceptores Wi-Fi, Bluetooth y RF.Permite que estos dispositivos manejen flujos de datos complejos necesarios para establecer y mantener enlaces de comunicación inalámbrica, que son parte integral de los dispositivos interconectados modernos.

Figura 13: Control del motor

En aplicaciones de control de motor, SPI se comunica con IC del controlador de motor para regular parámetros como la velocidad y la dirección.Esto es significativo en robótica, automatización industrial y sistemas de vehículos, donde el control motor preciso afecta directamente el rendimiento y la confiabilidad.

Figura 14: interfaces de audio

Para los sistemas de audio digital, SPI conecta microcontroladores a códecs de audio o convertidores digitales a analógicos (DAC), asegurando una transmisión de audio digital sin problemas.

Figura 15: Sistemas de control industrial

SPI admite sistemas de control industrial al vincular los controladores lógicos programables (PLC) con sensores y actuadores.Esto es dinámico para el monitoreo y el control en tiempo real de los procesos industriales, mejorando la eficiencia operativa y la seguridad.

Figura 16: Sistemas de adquisición de datos

En los sistemas de adquisición de datos, SPI interfaces con convertidores analógicos a digitales (ADC) y convertidores digitales a analógicos (DAC) para una conversión de señal precisa.Esto es útil para aplicaciones que requieren un monitoreo y control precisos de los procesos físicos a través de sistemas digitales.

Figura 17: Electrónica automotriz

En tecnologías automotrices, SPI permite la comunicación entre microcontroladores y varios subsistemas vehiculares, incluidos sensores, actuadores y unidades de control electrónico (ECU).Esta integración es necesaria para administrar las funciones del motor, el diagnóstico y los sistemas de información y entretenimiento, contribuyendo a la seguridad general y la funcionalidad de los vehículos modernos.

Figura 18: Sistemas integrados

La simplicidad y eficiencia de SPI lo hacen ideal para sistemas integrados, donde el espacio y la eficiencia energética son a menudo limitaciones.Su capacidad para interactuar sin problemas con varios dispositivos periféricos respalda su uso generalizado en aplicaciones integradas en múltiples industrias.

Conclusión

Para decirlo brevemente, el protocolo de interfaz periférica en serie (SPI) se destaca como una herramienta requerida en las industrias electrónicas y informáticas, impulsadas por sus capacidades de transferencia de datos de alta velocidad y opciones de configuración flexibles.Desde redes de sensores simples hasta tareas complejas de memoria y comunicación, la arquitectura de SPI atiende a un amplio espectro de aplicaciones, lo que lo convierte en una opción preferida para los diseñadores que buscan soluciones de comunicación de datos eficientes, escalables y confiables.Si bien enfrenta desafíos como el aumento de los requisitos de la línea de señal y la necesidad de comunicaciones precisas controladas con maestría, los beneficios de SPI, incluida su simplicidad en los requisitos de hardware y la capacidad de administrar múltiples periféricos de manera eficiente, superan significativamente estas limitaciones.A medida que los dispositivos electrónicos continúan evolucionando hacia una mayor complejidad y mayores demandas de rendimiento, el papel de SPI está listo para expandirse, incrustándose aún más como un componente inseguro en el desarrollo de soluciones tecnológicas innovadoras en todas las industrias.Las mejoras continuas en las configuraciones SPI, como el modo Quad IO, subrayan la adaptabilidad y el potencial del protocolo para enfrentar desafíos tecnológicos futuros, asegurando su continua relevancia y utilidad para avanzar en los marcos de comunicación digital.

Preguntas frecuentes [Preguntas frecuentes]

1. ¿Cuáles son los 4 modos de protocolo SPI?

El protocolo SPI funciona en cuatro modos, que se distinguen por su configuración de Polaridad de reloj (CPOL) y Fase de reloj (CPHA):

Modo 0 (CPOL = 0, CPHA = 0): el reloj se integra a bajo, y los datos se capturan en el borde ascendente del reloj y se propagan en el borde que cae.

Modo 1 (CPOL = 0, CPHA = 1): el reloj se integra a bajo, pero los datos se capturan en el borde que cae y se propaga en el borde ascendente.

Modo 2 (CPOL = 1, CPHA = 0): el reloj se integra en alto, con datos capturados en el borde que cae y se propagó en el borde ascendente.

Modo 3 (CPOL = 1, CPHA = 1): el reloj se siente en alto y los datos se capturan en el borde ascendente y se propagan en el borde que cae.

2. ¿Cuál es el formato de interfaz SPI?

La interfaz SPI generalmente consta de cuatro líneas principales:

Master Out Slave en (MOSI): la línea utilizada por el dispositivo maestro para enviar datos al esclavo.

Maestro en Slave Out (miso): la línea sobre la cual el esclavo envía datos al maestro.

Reloj (SCK): controlado por el maestro, esta línea sincroniza la transmisión de datos.

SECLET SELECCIÓN (SS): esta línea, impulsada por el maestro, selecciona el dispositivo esclavo activo.

3. ¿Cuál es la diferencia entre Serial y SPI?

La principal diferencia entre la comunicación en serie (como UART) y SPI está en su configuración y complejidad.La comunicación en serie generalmente usa dos cables (transmitir y recibir) y no requiere una línea de reloj ya que la sincronización de datos está integrada en el flujo de datos.En contraste, SPI es una estructura similar a un bus con una línea de reloj separada (SCK) y líneas de datos distintas para enviar y recibir (MOSI y MISO).Esto hace que SPI sea más rápido, pero requiere más líneas y una gestión cuidadosa de dispositivos de esclavos con la línea SS.

4. ¿Cuántos cables se usan en la comunicación SPI?

SPI Communication usa cuatro cables:

Mosi (maestro fuera de esclavo)

MISO (maestro en esclavo)

SCK (reloj en serie)

SS (Slave Select)

5. ¿Cómo conectar dispositivos SPI?

Para conectar dispositivos SPI, siga estos pasos:

Conecte el Mosi del maestro al Mosi de cada esclavo.

Conecte el miso del maestro al miso de cada esclavo.

Conecte el SCK del maestro al SCK de cada esclavo.

El pin SS de cada esclavo debe conectarse individualmente a una salida SS única en el maestro.

Las líneas terrestres deben ser comunes entre todos los dispositivos para garantizar la integridad de la señal.

Acerca de nosotros

ALLELCO LIMITED

Lee mas

Consulta rápida

Envíe una consulta, responderemos de inmediato.

Navegar por el mundo de los motores trifásicos: tipos, funciones e información operativa

en 22/06/2024

¿Qué es RF y por qué lo usamos?

en 20/06/2024

Publicaciones populares

-

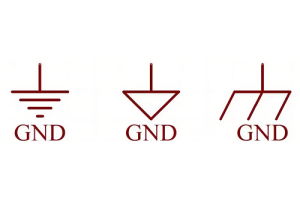

¿Qué es GND en el circuito?

en 01/01/1970 3328

-

Guía del conector RJ-45: códigos de color del conector RJ-45, esquemas de cableado, aplicaciones R-J45, hojas de datos RJ-45

en 01/01/1970 2854

-

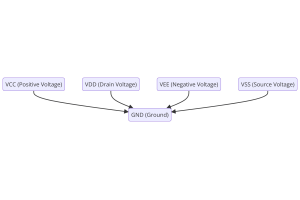

Comprensión de los voltajes de la fuente de alimentación en Electronics VCC, VDD, VEE, VSS y GND

en 21/11/0400 2791

-

Tipos de conector de fibra: SC vs LC y LC vs MTP

en 01/01/1970 2284

-

Comparación entre DB9 y RS232

en 01/01/1970 1901

-

¿Qué es una batería LR44?

La electricidad, esa fuerza ubicua, impregna en silencio todos los aspectos de nuestra vida diaria, desde dispositivos triviales hasta equipos médicos potencialmente mortales, juega un papel silencioso.Sin embargo, realmente comprender esta energía, especialmente cómo almacenarla y producirla de manera eficiente, no es una tarea fácil.Es en este fondo que este artículo se centrará en un tipo...en 01/01/1970 1858

-

¿Qué es RF y por qué lo usamos?

La tecnología de radiofrecuencia (RF) es una parte clave de la comunicación inalámbrica moderna, lo que permite la transmisión de datos a largas distancias sin conexiones físicas.Este artículo profundiza en los conceptos básicos de RF, explicando cómo la radiación electromagnética (EMR) hace posible la comunicación de RF.Exploraremos los principios de EMR, la creación y el control de l...en 01/01/1970 1845

-

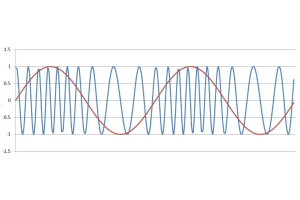

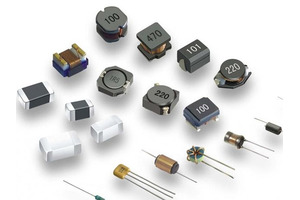

Comprender los fundamentos: resistencia a la inductancia y capacidad

En la intrincada danza de la ingeniería eléctrica, un trío de elementos fundamentales toma el centro del escenario: inductancia, resistencia y capacitancia.Cada uno tiene rasgos únicos que dictan los ritmos dinámicos de los circuitos electrónicos.Aquí, nos embarcamos en un viaje para descifrar las complejidades de estos componentes, para descubrir sus distintos roles y usos prácticos dentr...en 01/01/1970 1831

-

Guía integral de batería CR2430: especificaciones, aplicaciones y comparación con las baterías CR2032

¿Qué es la batería CR2430?Beneficios de las baterías CR2430NormaAplicaciones de batería CR2430CR2430 equivalenteCR2430 vs CR2032Batería CR2430 TamañoQué buscar al comprar el CR2430 y los equivalentesHoja de datos pdfPreguntas frecuentes Las baterías son el corazón de pequeños dispositivos electrónicos.Entre los muchos tipos disponibles, las células de monedas juegan un papel crucial, ...en 01/01/1970 1827

-

Guía completa de HFE en transistores

Los transistores son componentes cruciales en dispositivos electrónicos modernos, lo que permite la amplificación y el control de la señal.Este artículo profundiza en el conocimiento que rodea HFE, incluida cómo seleccionar el valor de HFE de un transistor, cómo encontrar HFE y la ganancia de diferentes tipos de transistores.A través de nuestra exploración de HFE, obtenemos una comprensió...en 21/11/5600 1825