Guía innovadora de Flip-Flops: Análisis de tablas de verdad, mecanismos y aplicaciones estratégicas

Este artículo explora la arquitectura, la operación y las diversas aplicaciones del flip-flop JK, comenzando desde su estructura básica y las relaciones de entrada-salida, a través de una mecánica operativa detallada, a sus implementaciones estratégicas en sistemas digitales complejos.El discurso se extiende a distinguir entre las variantes activadas por el borde y el nivel, analizando sus respectivas utilidades en entornos sincrónicos y asincrónicos.Catalogar

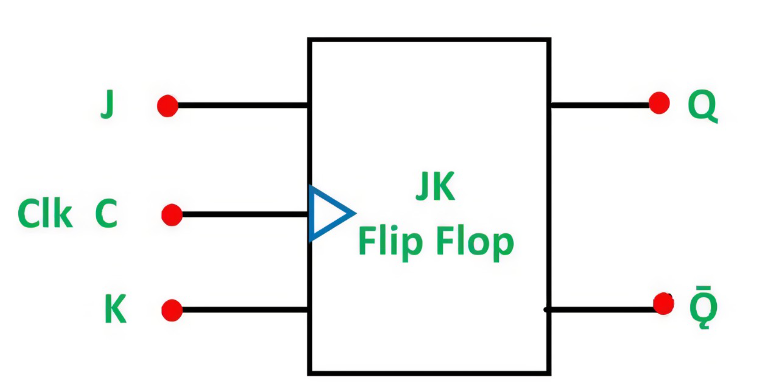

Figura 1: JK Flip-flop

Conceptos básicos de JK Flip-flop

El JK Flip-Flop es un componente básico en Electrónica Digital, diseñado para almacenar un solo poco de información.Se basa en el flip-flop más simple al agregar retroalimentación, lo que ayuda a prevenir errores conocidos como "condiciones de carrera", donde la salida se vuelve inestable.

Este flip-flop tiene dos entradas principales, j (set) y k (reinicio), y dos salidas: q y su complemento, q '.Estas salidas reflejan continuamente el estado actual y su opuesto, lo que permite que el circuito se ajuste y responda a los cambios de entrada en tiempo real.

El Flip-Flop JK funciona de manera específica en función de los valores de entrada:

• Cuando tanto J como K son 0: El flip-flop posee su estado actual.No se producen cambios.

• Cuando tanto J como K son 1: El flip-flop alterna su estado.Si Q es 0, se convierte en 1;Si Q es 1, cambia a 0. Esta acción de alternar es una característica clave que distingue el flip-flop JK de diseños más simples.

• Cuando J es 1 y K es 0: El flip-flop establece su estado, haciendo que Q sea igual a 1.

• Cuando J es 0 y K es 1: El flip-flop se restablece, haciendo Q igual a 0.

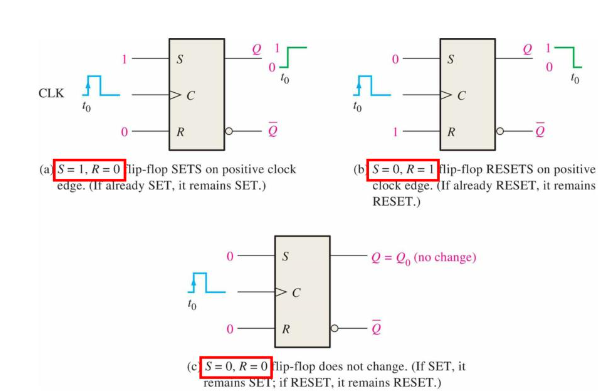

Operación de la flip-flop JK

El JK Flip-Flop juega un papel clave en los circuitos digitales al administrar la memoria y el tiempo a través de una respuesta coordinada a las señales de entrada y los pulsos de reloj.Su operación depende en gran medida del momento de las entradas J y K en relación con la señal del reloj, que determina cómo cambian los estados de salida (Q y Q̅).Esta sincronización garantiza que el flip-flop se comporte previsiblemente en varias aplicaciones de circuito.El flip-flop se basa en NAND o ni puertas para administrar estos cambios de estado.

Sosteniendo el estado actual- Cuando las entradas J y K son bajas (0), el flip-flop mantiene su estado actual.Las puertas lógicas "bloquean" las salidas, asegurando que se mantenga el estado anterior (alto o bajo).Esta función de retención es grave en aplicaciones donde los datos deben permanecer estables hasta que un cambio específico sea imprescindible.

Configuración de la salida alta (Estado establecido) -Cuando ocurre el pulso del reloj y J es alto (1) mientras que K permanece bajo (0), las puertas lógicas se ajustan para establecer el flip-flop.Esto impulsa la salida Q a un estado alto (1).Esto es útil en situaciones en las que el circuito necesita activar una salida alta, por ejemplo, activar un dispositivo o almacenar un "1" en la memoria.

Limpiar la salida baja (estado de reinicio) - Si J es bajo (0) y K es alto (1) en el momento de un pulso de reloj, el flip-flop pasa a un estado de reinicio, lo que obliga a Q a bajar (0).Esta acción de reinicio a menudo se usa en circuitos que necesitan un estado predeterminado o claro después de completar una operación, como la limpieza de datos de la memoria.

Alternando la salida - La característica única del flip-flop surge cuando tanto J como K son altos (1).Cuando llega el pulso del reloj, el flip-flop alterna, cambiando la salida de su estado actual a uno opuesto.Si Q es alto, se vuelve bajo, y si Q es bajo, se vuelve alto.Esta función de alternativa insiste en aplicaciones como contadores o dispositivos que necesitan alternarse entre estados automáticamente.

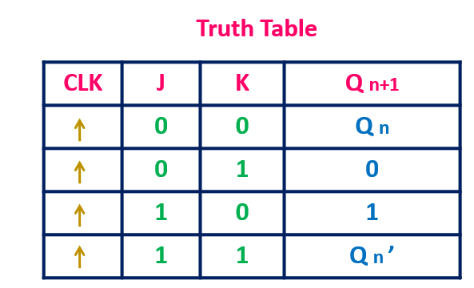

Figura 2: Table de verdad JK Flip-Flop

Análisis de mesa de verdad de JK Flip-Flop

La tabla de verdad del flip-flop JK es una herramienta clave para visualizar cómo reacciona a diferentes señales de entrada sincronizadas con pulsos de reloj.Esta tabla ayuda tanto en el diseño como en la resolución de los circuitos digitales al mostrar cómo cambian las salidas del flip-flop en función de diversas condiciones de entrada.

• Tanto j como k bajo (j = 0, k = 0): Cuando ambas entradas son 0, el flip-flop contiene su estado actual.Ya sea que Q sea alto o bajo, permanece sin cambios.Esto es notable para los circuitos donde se busca retención de datos estables, como elementos en memoria, donde preservar el estado actual es adecuado hasta que se active un cambio específico.

• j alto, k bajo (j = 1, k = 0): Cuando J es 1 y K es 0, el flip-flop establece la salida Q a alto (1).Esta condición de configuración es útil en aplicaciones que requieren un desencadenante preciso para activar una operación, como encender un dispositivo o iniciar una secuencia en un circuito lógico.

• J bajo, k alto (j = 0, k = 1): Con J en 0 y K en 1, el flip-flop se restablece, haciendo Q bajo (0).Esta función de reinicio es grave en los sistemas que necesitan volver a un estado predeterminado, como al borrar los datos o inicializar un proceso.

• Tanto J como K High (J = 1, K = 1): Cuando ambas entradas son altas, el flip-flop alterna su estado.Si Q es alto, se vuelve bajo, y si Q es bajo, cambia a alto.Este comportamiento de alternativa es sustancial para los dispositivos que necesitan alternarse entre los estados, como en divisores de frecuencia o contadores.

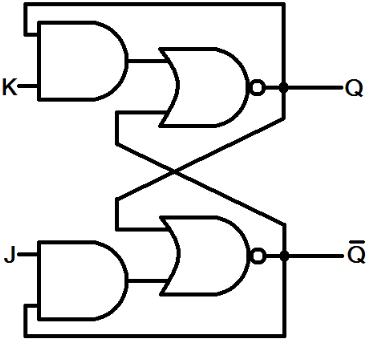

Figura 3: JK Latch

Información sobre la operación de JK Latch y usa

El pestillo JK funciona de manera similar al flip-flop JK pero sin la necesidad de una señal de reloj.En lugar de esperar un borde de reloj, el pestillo JK responde continuamente a los cambios de entrada, lo que lo hace "sensible al nivel".Esto significa que mientras las entradas (j y k) sean estables, la salida cambiará en tiempo real, ofreciendo comentarios inmediatos basados en las condiciones de entrada.

A diferencia del flip-flop JK activado por el borde, que actualiza su salida solo cuando la señal del reloj cambia (de baja a alta o viceversa), el pestillo JK ajusta su salida al instante a medida que las entradas cambian.Esta capacidad de respuesta constante en tiempo real es valiosa en escenarios en los que se desea una acción inmediata sin el retraso causado por la sincronización del reloj.

Filtros de ruido: En los circuitos digitales que necesitan filtrar rápidamente el ruido no deseado, la reacción instantánea de JK Latch a los cambios de entrada es influyente.Debido a que no espera un pulso de reloj, puede ajustar la salida tan pronto como se detecta el ruido, evitando retrasos en la corrección de la señal.

Elementos de memoria simple: El pestillo JK puede servir como una unidad de memoria básica en sistemas que no requieren un control complejo con reloj.Dado que el pestillo mantiene la salida estable siempre que las entradas no cambien, mantiene efectivamente el estado actual, lo que es útil para los circuitos que necesitan retener información sin la sobrecarga de operaciones con reloj.

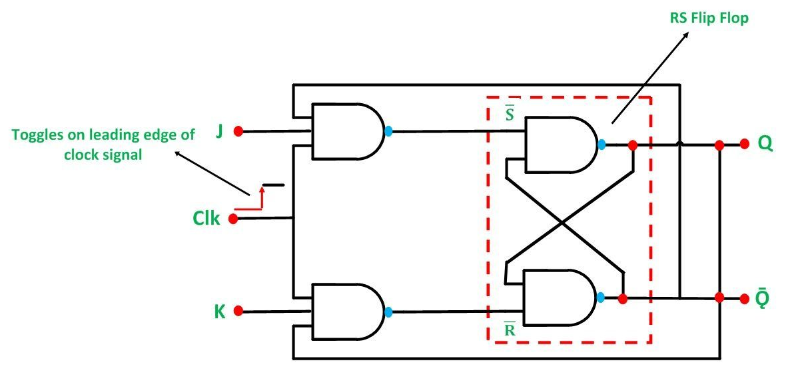

Figura 4: Análisis del diagrama de tiempo para el flip-flop JK

Análisis del diagrama de tiempo de las chanclas JK

Un diagrama de tiempo del flip-flop JK proporciona una desglose visual de cómo la salida responde a diferentes entradas, sincronizadas con las transiciones de pulso del reloj.Este diagrama muestra la relación entre la señal del reloj (CLK) y las entradas (J y K), y cómo influyen colectivamente en las salidas (Q y Q ').Ayuda a mapear el comportamiento del flip-flop en los estados secuenciales, lo que facilita la comprensión de su operación.

En primer lugar, el diagrama destacan que las salidas se actualizan solo en los bordes ascendentes o descendentes del pulso del reloj.Esta característica, conocida como activación de borde, es dominante para la operación del flip-flop JK.Muestra que incluso si las entradas J y K cambian, la salida permanece sin cambios hasta que ocurra el borde del reloj, asegurando transiciones predecibles y estables.

Luego, a medida que el diagrama asigna las variaciones de las entradas J y K, visualmente Demuestra cómo cada combinación de entrada afecta la salida. Por ejemplo, cuando tanto J como K son bajos (0), la salida contiene su estado actual.Cuando J es alto y K es bajo, la salida se establece.Esta representación visual clara ayuda a los usuarios a comprender cómo reacciona el flip-flop a diferentes combinaciones de entrada en tiempo real.

Finalmente, El diagrama de tiempo muestra claramente las transiciones entre diferentes estados de salida, ya sea retención, configuración, restablecimiento o alternativa.Cada cambio de estado está ligado directamente a las condiciones de entrada y al borde del reloj, que muestra una relación de causa y efecto que es focal para diseñar y solucionar circuitos.

Aplicaciones versátiles de chanclas JK

Las chanclas JK son componentes centrales en una amplia gama de sistemas digitales, conocidos por su flexibilidad y confiabilidad.Su capacidad para manejar operaciones lógicas complejas los hace requisitos en varias aplicaciones clave, que incluyen:

Figura 5: Almacenamiento de memoria

Las chanclas JK se usan comúnmente para almacenar bits de datos individuales, lo que los convierte en elementos fundamentales en matrices de memoria y registros.Cada flip-flop contiene un bit, asegurando un almacenamiento de datos confiable, lo cual es beneficioso en el diseño de sistemas de memoria más grandes.

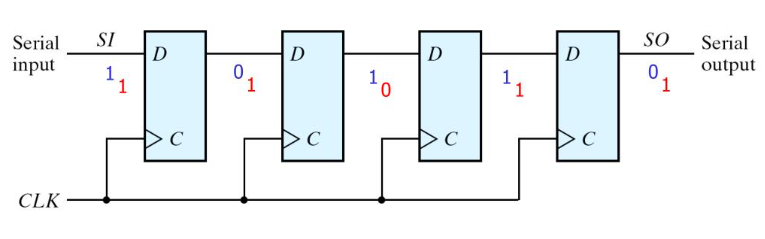

Figura 6: Contadores y registros de cambio

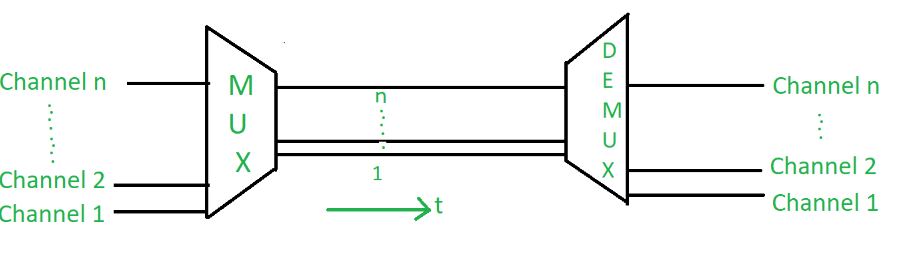

Las chanclas JK son dinámicas en las operaciones de secuenciación.Se usan ampliamente en contadores para contar eventos o pulsos y en registros de turno para convertir los datos en serie en formatos paralelos.Esto los hace útiles para administrar y manipular datos en diferentes etapas de un proceso, como en los sistemas de comunicación.

Figura 7: División de frecuencia

En el procesamiento de señales, las flipas JK a menudo se usan para la división de frecuencia.Al alternar su estado con cada pulso de reloj, dividen la frecuencia de la señal de entrada, creando una señal de reloj más lenta y manejable.Esto es notable en aplicaciones como la gestión de la señal del reloj, donde se desea el control de sincronización.

Figura 8: Sincronización

Los flip-flops JK ayudan a sincronizar múltiples procesos digitales asegurando que diferentes partes de un sistema funcionen juntas de manera coordinada.Se aseguran de que varios componentes respondan correctamente a las señales cronometradas, manteniendo todo el sistema sincronizado.

Figura 9: JK Flip-flop: activado por el borde y activado por el nivel

Diferentes tipos de chanclas JK

Las chanclas JK están disponibles en dos tipos principales: activados por el borde y activados por el nivel, cada uno diseñado para diferentes requisitos operativos.

Flip-Flops JK activados por el borde: Cambie su estado solo en puntos específicos, cuando la señal del reloj pasa de baja a alta (borde ascendente) o alto a bajo (borde caída).Esta característica los hace ideales para sistemas donde el tiempo preciso es insistente.Debido a que los cambios en el estado ocurren exactamente en el borde del reloj, estas chanclas aseguran que todas las actualizaciones ocurran en sincronización con el pulso del reloj.Este comportamiento predecible es dinámico en entornos estrechamente controlados, como relojes digitales, registros y la mayoría de los circuitos secuenciales.Aquí, el momento de cada cambio es grave para mantener la estabilidad del sistema y garantizar que las operaciones se sincronizen.

Flip-flops JK activados por el nivel: operar de manera diferente, reaccionando a la señal de entrada siempre que la señal del reloj esté en un nivel particular, ya sea alto o bajo.No esperan una transición de reloj específica.En cambio, mientras la entrada cumpla con las condiciones requeridas, el flip-flop cambiará los estados.Este comportamiento hace que las chanclas activadas por el nivel sean más adecuadas para los sistemas asincrónicos, donde las entradas pueden no alinearse con un pulso de reloj regular.Proporcionan flexibilidad en los sistemas donde las entradas son impredecibles o llegan a intervalos irregulares, como en ciertas tareas de procesamiento de señales o sistemas de monitoreo que deben reaccionar inmediatamente a las entradas cambiantes.

Pros y contras de JK Flip-flop

Las chanclas JK ofrecen varios beneficios, pero también vienen con algunas compensaciones que deben pesar cuidadosamente al diseñar sistemas digitales.

|

Pros |

|

|

Versatilidad |

Las chanclas JK son altamente flexibles y pueden

ser utilizado en varios circuitos digitales como almacenamiento de memoria, contadores y

Sistemas de control.Pueden alternar, establecer o restablecer según las diferentes entradas

condiciones, haciéndolos adecuados para una amplia gama de aplicaciones que

requiere un control preciso sobre las transiciones de estado. |

|

Mecanismo de autocorrección |

Una de las características destacadas de JK

Flip-flops es su bucle de retroalimentación incorporado, que ayuda a corregir lógico

estados dinámicamente.Esta autocorrección asegura que el circuito permanezca

Estable durante la operación, incluso cuando las entradas cambian rápidamente. |

|

Mitigación de condición de carrera |

A diferencia de las chanclas más simples, las chanclas JK

están diseñados para prevenir las condiciones de la carrera, situaciones en las que se convierte la salida

inestable debido a señales de entrada conflictivas.Esta capacidad de mantener

La salida constante, incluso en cambios de entrada rápidos y secuenciales, mejora el

confiabilidad del circuito. |

|

Contras |

|

|

Diseño complejo |

Las chanclas JK son más complicadas que

Flip-flops básicos.Su diseño requiere puertas lógicas adicionales y entrada

monitoreo, que puede hacer que el circuito sea más difícil de diseñar y

Solución de problemas, especialmente en sistemas donde se prefiere la simplicidad. |

|

Retraso de propagación |

La activación interna utilizada para administrar el estado

Las transiciones introducen un retraso en la forma en que se pueden procesar las señales rápidas.En

Aplicaciones de alta velocidad, este retraso puede afectar el tiempo general y la velocidad

El rendimiento del circuito. |

|

Mayor consumo de energía |

Debido a su complejidad y a la necesidad de

Controle constantemente las condiciones de entrada, JK Flip-flops consumen más energía

en comparación con las chanclas más simples.En sistemas más grandes o de potencia sensible

Aplicaciones, esta mayor demanda de energía puede convertirse en un inconveniente |

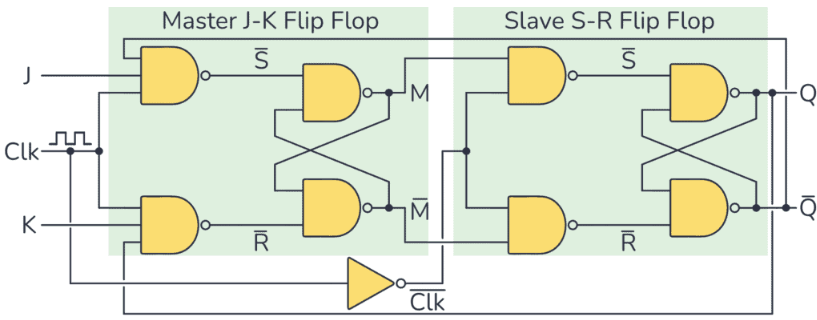

Figura 10: Master-Slave JK Flip-flop

Decodificación de la flip-flop de JK de JK

El Flip-Flop JK Master-Slave está diseñado para resolver la condición de carrera que se encuentra en las flipas JK estándar utilizando un proceso de dos pasos para administrar entradas y salidas de manera más eficiente.

La primera etapa, llamada etapa maestra, captura los valores de entrada cuando la señal del reloj alcanza un borde específico, ya sea subiendo o disminuyendo.En este punto, los datos de entrada están bloqueados, lo que significa que los cambios adicionales a las entradas no afectan el estado capturado hasta el siguiente ciclo de reloj.Esta etapa asegura que el flip-flop registre la entrada correcta sin ser influenciada por ningún cambio posterior durante el mismo ciclo de reloj.

Después de que se completa la etapa maestra, el escenario esclavo entra en juego.Esta etapa actualiza la salida en función de los datos capturados por la etapa maestra, pero solo en el siguiente borde del reloj.Al separar la captura de entrada de la actualización de salida, la etapa esclava asegura que la salida permanezca estable hasta que la etapa maestra haya procesado completamente la entrada.Esto evita cualquier cambio prematuro o no deseado en la salida durante el ciclo de reloj.

¿Por qué es importante la configuración del esclavo maestro?

El proceso de dos etapas estabiliza el funcionamiento del flip-flop JK, evitando oscilaciones o fluctuaciones no deseadas que pueden ocurrir en configuraciones más simples, especialmente cuando ambas entradas se mantienen altas.Al desacoplar el procesamiento de entrada del cambio de salida, la configuración del esclavo maestro garantiza que las salidas sigan siendo predecibles y estables, incluso en situaciones donde el tiempo es valioso.

Abordar la carrera alrededor de la condición en JK Flip-Flops

Las condiciones de raza se producen en las chanclas JK cuando ambas entradas, J y K, son altas, y la señal del reloj permanece activa durante demasiado tiempo.Esto conduce al alternativo continuo de las salidas, lo que puede causar un comportamiento errático e interrumpir la confiabilidad del circuito.

La configuración de maestro-esclavo utiliza un proceso de dos etapas para evitar problemas de carrera.La etapa maestra captura los valores de entrada en el borde del reloj y los bloquea. La etapa esclava actualiza las salidas en el siguiente borde del reloj, asegurando que la salida no cambie hasta que las entradas se procesen completamente.Este enfoque evita efectivamente que la salida alternara incontrolablemente, incluso si las entradas permanecen altas durante un período prolongado.

Otro método para evitar condiciones de carrera es ajustar la duración del pulso del reloj.Al hacer el pulso del reloj más corto que el retraso de propagación del flip-flop, puede asegurarse de que el estado no cambie más de una vez dentro del mismo ciclo de reloj.Esto evita que el flip-flop alterne repetidamente durante un solo ciclo, estabilizando la salida.

Dinámica de conmutación en chanclas JK

El comportamiento de conmutación de un flip-flop JK está impulsado en gran medida por el momento de la señal del reloj y los niveles de entrada (J y K).El estado de cambio de flip-flop en función de las entradas presentes en el borde positivo de la señal del reloj.En este momento peligroso, el flip-flop evalúa las entradas y actualiza su salida en consecuencia.

Cuando la señal del reloj alcanza el borde ascendente, el flip-flop JK lee los estados actuales de las entradas J y K.Dependiendo de sus valores, el flip-flop mantendrá, establecerá, restablecerá o alternará su salida.

Relojes digitales: La precisión es todo en los relojes digitales, y las flipps de JK ayudan a mantener esta precisión al garantizar que los cambios en el estado solo ocurran a intervalos precisos de reloj.

Probadores lógicos secuenciales: En los sistemas que prueban la funcionalidad de los circuitos lógicos, los flip-flops JK juegan un papel en la verificación de que cada componente responde correctamente a señales cronometradas específicas.

Otros sistemas sensibles al tiempo: En diversas aplicaciones digitales donde el tiempo es arriesgado, como los sistemas de comunicación o las unidades de procesamiento de datos, el Flip-Flop JK asegura que las transiciones de estado ocurran sincronizadas con el reloj, evitando los errores de tiempo.

Conclusión

El JK Flip-Flop se destaca como un elemento final en el diseño de circuitos digitales, que ofrece una combinación de versatilidad y precisión desesperada por una amplia gama de aplicaciones que van desde el almacenamiento de memoria hasta la división de frecuencia y la sincronización de procesos digitales.Su capacidad para mitigar las condiciones de carrera a través de configuraciones innovadoras, como la disposición del esclavo maestro, subraya su adaptabilidad para resolver los desafíos de diseño inherentes.Igualmente, el papel grave del flip-flop para garantizar las transiciones estatales precisas resalta su naturaleza necesaria en la creación y mantenimiento de sistemas digitales confiables y eficientes.A medida que avanza la tecnología, los diseños y aplicaciones en evolución del flip-flop JK continúan siendo clave para empujar los límites de la electrónica digital hacia arquitecturas más sofisticadas y robustas.

Preguntas frecuentes [Preguntas frecuentes]

1. ¿Cuáles son las aplicaciones de JK Flip Flop?

El JK Flip-flop se usa ampliamente en electrónica digital para una variedad de tareas:

Aplicaciones de tiempo: Puede servir como un elemento de retraso o un temporizador cuando está conectado en ciertas configuraciones.

Contadores y registros: Al alternar su estado con cada pulso de reloj, se usa en el diseño de varios contadores y registros de cambio que son lo último en circuitos lógicos secuenciales.

Almacenamiento de memoria: Proporciona una unidad básica de almacenamiento de memoria, útil para almacenar bits en aplicaciones computacionales.

2. ¿Cómo funciona un JK Flip-flop con una tabla de verdad?

Un JK Flip-flop tiene dos entradas (J y K) y una señal de reloj.Su operación varía en función de los estados de entrada, sincronizados con el reloj:

• J = 0, k = 0: la salida no cambia.

• J = 0, k = 1: la salida se restablece a 0.

• J = 1, k = 0: la salida se establece en 1.

• J = 1, k = 1: la salida se alza (es decir, si era 0, se convierte en 1 y viceversa).

3. ¿Qué es JK Flip Flop y está funcionando?

Un flip-flop JK combina las propiedades de las flip-flops Sr y T.Evita la condición "prohibida" observada en las flipps de SR mediante el uso de las entradas JK de manera efectiva:

El estado del flip-flop está controlado por las entradas J y K, que determinan si la salida debe mantener, restablecer, establecer o alternar, sincronizar con el borde ascendente o descendente del pulso del reloj.

4. ¿Cuáles son las aplicaciones de pestillos y chanclas?

Almacenamiento de datos: Los pestillos y las chanclas son graves para el almacenamiento de datos dentro de registros y matrices de memoria.

División de frecuencia: Utilizado en divisores de frecuencia debido a su capacidad para cambiar los estados en los bordes del reloj, a la mitad la frecuencia con cada etapa de una serie.

Máquinas de estado: Básico en el diseño de máquinas de estado finito que se utilizan para implementar circuitos de lógica y control secuencial.

Desacreditación: Se utiliza para estabilizar las señales de los interruptores y botones mecánicos, asegurando transiciones simples y limpias.

5. ¿Para qué se usan las chanclas?

Almacenamiento binario: Cada flip-flop almacena un poco de datos, lo que los convierte en bloques de construcción para dispositivos de almacenamiento binarios.

Divisores de reloj: Dividan la frecuencia del reloj de entrada por dos, útil en relojes digitales y aplicaciones de tiempo.