Comprensión de las características de AD9959 para el procesamiento de señales

El AD9959 es un sintetizador digital potente y flexible que ofrece control sobre la frecuencia, la fase y la amplitud en cuatro canales independientes.Este artículo cubre las características clave, las especificaciones técnicas y las aplicaciones comunes del AD9959, lo que le facilita la comprensión de cómo se puede usar este dispositivo en varias configuraciones.Ya sea que esté buscando crear osciladores locales ágiles o sincronizar sistemas complejos como radares de matriz Phased, el AD9959 proporciona la precisión y adaptabilidad necesarias para una amplia gama de proyectos.Al final de esta guía, tendrá una comprensión clara de cómo funciona el AD9959 y cómo se puede aplicar en diferentes campos.Catalogar

Descripción general de AD9959

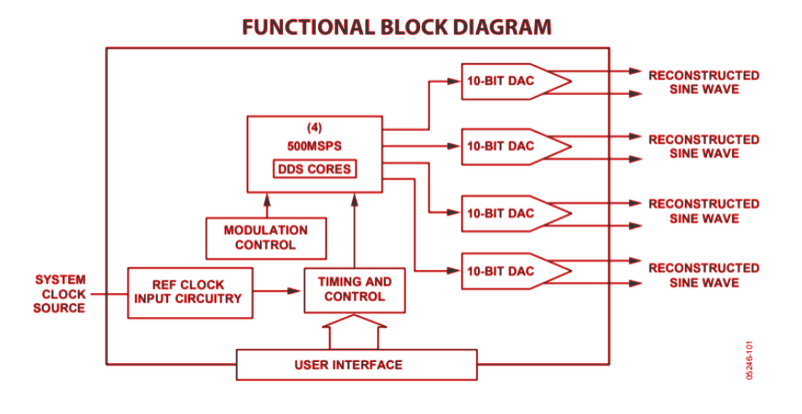

El AD9959 Ofrece cuatro núcleos de sintetizador digital directo, lo que le permite controlar la frecuencia, la fase y la amplitud de forma independiente para cada canal.Con la capacidad de manejar hasta 16 niveles de modulación, ya sea frecuencia, fase o amplitud, aporta flexibilidad a sus diseños.Dado que todos los canales comparten el mismo reloj del sistema, se mantienen sincronizados, asegurando una operación suave en múltiples canales.Además, si está trabajando con más de un AD9959, puede sincronizar fácilmente varios dispositivos, lo que lo hace ideal para configuraciones complejas.

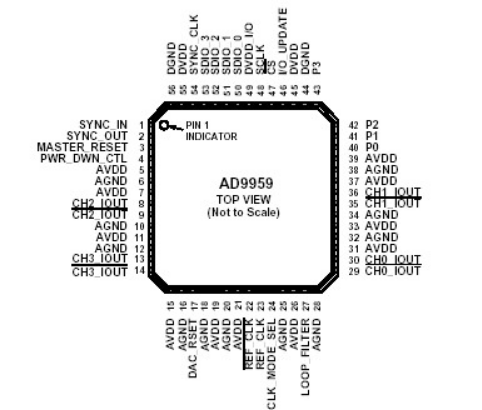

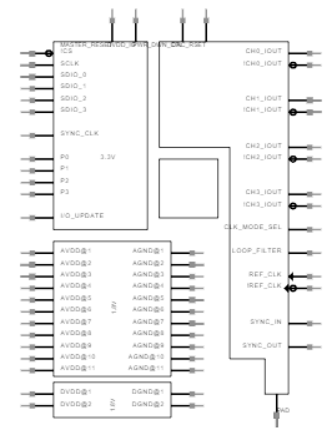

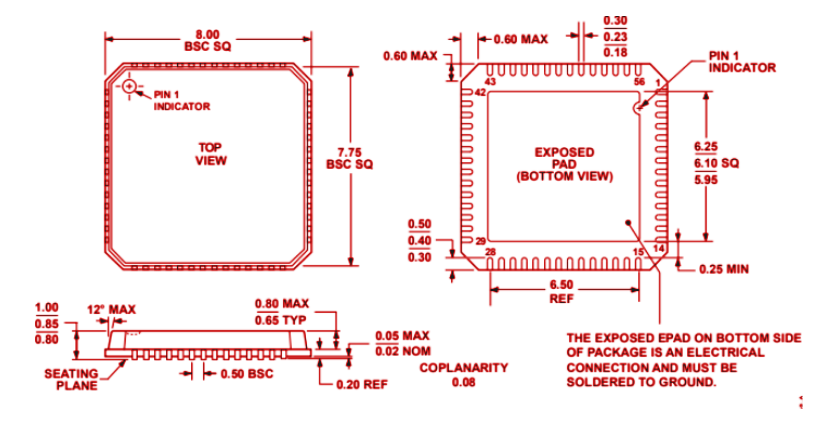

Diagrama de Pinout AD9959

| Pin No. | Mnemotécnico | E/S | Descripción |

| 1 | Sinc_in | I | Se utiliza para sincronizar múltiples dispositivos AD9959.Se conecta al pin Sync_out del dispositivo maestro AD9959. |

| 2 | Sincronizar | O | Se utiliza para sincronizar múltiples dispositivos AD9959.Se conecta al pin Sync_in del dispositivo Slave AD9959. |

| 3 | Maestro_reset | I | Pin de reinicio alto activo.Afirmar que el PIN Master_reset obliga a los registros internos AD9959 a su estado predeterminado. |

| 4 | Pwr_dwn_ctl | I | Control de apagado externo. |

| 5, 7, 11, 15, 19, 21, 26, 31, 33, 37, 39 | Avdd | I | Pins de fuente de alimentación analógica (1.8V). |

| 6, 10, 12, 16, 18, 20, 25, 28, 32, 34, 38 | Agnd | I | Pins de tierra analógicos. |

| 44, 56 | DVDD | I | Pins de fuente de alimentación digital (1.8V). |

| 45, 55 | Dgnd | I | Pins de tierra de potencia digital. |

| 8 | CH2_IOUT | O | Outalidad DAC verdadera.Termina en AVDD. |

| 9 | CH2_IOUT | O | Salida de DAC complementaria.Termina en AVDD. |

| 13 | CH3_IOUT | O | Outalidad DAC verdadera.Termina en AVDD. |

| 14 | CH3_IOUT | O | Salida de DAC complementaria.Termina en AVDD. |

| 17 | Dac_rset | I | Establece la corriente de referencia para todos los DAC.Una resistencia de 1.91 kΩ (nominal) está conectada del pin 17 a Agnd. |

| 22 | Ref_clk | I | Control de reloj de referencia/oscilador complementario.Cuando el ref_clk se opera en modo de un solo extremo, este PIN debe desacoplarse a AVDD o AgND con un condensador de 0.1 µF. |

| 23 | Ref_clk | I | Entrada de reloj/oscilador de referencia.Cuando el ref_clk se opera en modo de un solo extremo, esta es la entrada.Consulte la sección Modos de operación para la configuración del reloj de referencia. |

| Pin No. | Mnemotécnico | E/S | Descripción |

| 24 | Clk_mode_sel | I | Pin de control para la sección del oscilador.PRECAUCIÓN: No conduzca este pin más allá de 1.8V.Cuando está alto (1.8V), la sección del oscilador está habilitado para aceptar un cristal como fuente Ref_Clk.Cuando está bajo, se omite la sección del oscilador. |

| 27 | Bucle_filter | I | Se conecta a la red de compensación cero externa del filtro de bucle PLL.Típicamente, la red consiste en una resistencia de 0Ω en serie con un condensador de 680pf vinculado a AVDD. |

| 29 | CH0_IOUT | O | Salida de DAC complementaria.Termina en AVDD. |

| 30 | CH0_IOUT | O | Outalidad DAC verdadera.Termina en AVDD. |

| 35 | CH1_IOUT | O | Salida de DAC complementaria.Termina en AVDD. |

| 36 | CH1_IOUT | O | Outalidad DAC verdadera.Termina en AVDD. |

| 40 a 43 | P0 a P3 | I | Los pasadores de datos utilizados para la modulación (FSK, PSK, Ask), para comenzar/detener los acumuladores de barrido o utilizar para aumentar/aumentar la amplitud de salida.Los datos son sincrónicos para el sync_clk (pin 54).Las entradas de datos deben cumplir con los requisitos de tiempo de configuración y retención de sync_clk.La funcionalidad de estos pines está controlada por los bits de configuración del pin de perfil (PPC) (FR1 [14:12]). |

| 46 | I/o_update | I | Un borde ascendente transfiere datos del búfer de puerto de E/S en serie a registros activos.I/O_UPDATE es sincrónico para el sync_clk (pin 54).I/O_UPDATE debe cumplir con los requisitos de tiempo de configuración y retención de sync_clk para garantizar un retraso de la tubería fijo de los datos a la salida DAC;De lo contrario, existe el período de sinc_clk de incertidumbre de la tubería.El ancho mínimo de pulso es un período Sync_Clk. |

| 47 | Cs \ | I | Seleccionar chip bajo activo.Permite múltiples dispositivos para compartir un bus de E/S común (SPI). |

| 48 | Sclk | I | Reloj de datos en serie para operaciones de E/S.Los bits de datos se escriben en el borde ascendente de SCLK y se leen en el borde que cae de SCLK. |

| 49 | Dvdd_i/o | I | Fuente de alimentación digital de 3.3V para puerto SPI y E/S digital. |

| 50 | Sdio_0 | E/S | Data PIN SDIO_0 está dedicado solo a la E/S del puerto serie. |

| 51, 52 | Sdio_1, sdio_2 | E/S | Pin de datos SDIO_1 y PIN de datos SDIO_2 se pueden usar para el puerto de E/S en serie o se usa para iniciar un aumento/aumento (RU/RD) de la amplitud de salida de DAC. |

| 53 | Sdio_3 | E/S | Pin de datos SDIO_3 se puede utilizar para el puerto de E/S en serie o para iniciar una reducción/reducción (RU/RD) de la amplitud de salida de DAC.En modos de un solo bit o 2 bits, SDIO_3 se usa para Sync_i/O.Si no se usa la función Sync_i/O, ata la tierra o la lógica 0. No permita que SDIO_3 flote en modos de un solo bits o 2 bits. |

| 54 | Sync_clk | O | El sync_clk se ejecuta en un cuarto la tasa de reloj del sistema;se puede deshabilitar.I/O_UPDATE o DATA (PIN 40 al PIN 43) es sincrónico para SYNC_CLK.Para garantizar un retraso de la tubería fijo de los datos a la salida DAC, I/O_UPDATE o datos (PIN 40 al PIN 43) debe cumplir con los requisitos de configuración y retener el tiempo al borde ascendente de SYNC_CLK;De lo contrario, ocurre el período de incertidumbre Sync_Clk. |

Descripción general del modelo AD9959 CAD

Símbolo AD9959

Huella AD9959

Diagrama detallado de bloques AD9959

AD9959 Especificaciones técnicas

Especificaciones técnicas, atributos, parámetros y partes comparables para Analog Devices Inc. AD9959BCPZ.

| Tipo | Parámetro |

| Estado del ciclo de vida | |

| Tiempo de entrega de fábrica | 8 semanas |

| Contactor | Estaño |

| Montar | Montaje en superficie |

| Tipo de montaje | Montaje en superficie |

| Paquete / estuche | Almohadilla expuesta 56-vfqfn, CSP |

| Número de alfileres | 56 |

| Temperatura de funcionamiento | -40 ° C a 85 ° C |

| Embalaje | Bandeja |

| Código JESD-609 | E3 |

| Código PBFree | No |

| Estatus de parte | Activo |

| Nivel de sensibilidad de humedad (MSL) | 3 (168 horas) |

| Número de terminaciones | 56 |

| Terminación | SMD/SMT |

| Código ECCN | EAR99 |

| Característica adicional | También requiere un suministro de 3.3V |

| Disipación de potencia máxima | 680MW |

| Voltaje - suministro | 1.71V a 1.96V |

| Posición terminal | PATIO |

| Forma terminal | Sin plomo |

| Temperatura máxima de reflujo (° C) | 260 |

| Voltaje de suministro | 1.8V |

| Terminal | 0.5 mm |

| Frecuencia | 500MHz |

| TIME @ peak reflow temperp (s) | 30 |

| Número de pieza base | AD9959 |

| Recuento de alfileres | 56 |

| Estado de calificación | No calificado |

| Voltaje de suministro operativo | 1.8V |

| Interfaz | De serie |

| Corriente de suministro operativo | 180 mA |

| Corriente de suministro nominal | 160 mA |

| Corriente de suministro máximo | 185 mA |

| UPS/UCS/Tipo de ICS periférico | |

| Número de bits | 10 |

| Tasa de muestreo | 500 MSPS |

| Exploración límite | No |

| Modo de baja potencia | Sí |

| Tasa de conversión | 500 MSPS |

| Número de convertidores D/A | 4 |

| Resolución (bits) | 10 B |

| Ancho de palabras de ajuste (bits) | 32 B |

| Altura | 830 μm |

| Longitud | 8 mm |

| Ancho | 8 mm |

| Llegar a SVHC | Sin SVHC |

| Estado de ROHS | ROHS3 Cumplante |

| Plomo libre | Contiene plomo |

Características clave AD9959

4 canales DDS sincronizados a 500 msps

El AD9959 proporciona cuatro canales sincronizados del sintetizador digital directo (DDS), todos operando a hasta 500 MSP.Esto le permite generar señales precisas en múltiples canales mientras se mantiene la sincronización, lo que es especialmente útil cuando se trabaja en proyectos que requieren múltiples salidas que funcionan sin problemas.

Frecuencia independiente, fase y control de amplitud

Cada uno de los cuatro canales DDS ofrece un control independiente sobre la frecuencia, la fase y la amplitud.Esto le permite ajustar cada canal para adaptarse a diferentes necesidades, lo que le brinda flexibilidad en el manejo de varios parámetros de señal.

Latencias emparejadas para cambios de frecuencia, fase y amplitud

El AD9959 asegura que los cambios en la frecuencia, la fase y la amplitud se sincronizan entre los canales.Esto significa que cuando ajusta un parámetro, el cambio ocurre simultáneamente en todos los canales, lo que le ayuda a mantener salidas consistentes sin retraso.

Excelente aislamiento de canal a canal

Con más de 65 dB de aislamiento de canal a canal, el AD9959 minimiza la interferencia entre los canales.Esto asegura que las señales generadas en cada canal sean limpias y distintas, proporcionando un rendimiento de mayor calidad en sus diseños.

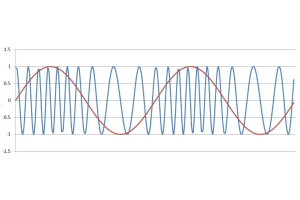

Capacidad de barrido lineal

El AD9959 admite la frecuencia lineal, la fase y el barrido de amplitud.Esta característica le permite hacer una transición sin problemas entre valores, lo que facilita la generación de señales que cambian gradualmente con el tiempo, lo que puede ser útil para fines de prueba y calibración.

Hasta 16 niveles de modulación de frecuencia, fase y amplitud

El dispositivo puede manejar hasta 16 niveles de modulación para la frecuencia, fase o amplitud.Este nivel de flexibilidad le permite implementar una variedad de esquemas de modulación, de simple a complejo, dependiendo de las necesidades de su proyecto.

Convertidores integrados de 10 bits digitales a analógicos (DACS)

Cada canal viene con su propio DAC integrado de 10 bits, lo que le permite convertir las señales digitales en salidas analógicas con precisión.Esto hace que el AD9959 sea una excelente opción cuando necesita una generación de señal analógica precisa en forma compacta.

Corrientes de gran escala de DAC de DAC individualmente programables

Puede programar la corriente a gran escala para cada DAC individualmente, lo que le brinda control sobre la potencia de salida de cada canal.Este nivel de personalización le permite optimizar el nivel de potencia para diferentes canales en función de sus requisitos específicos.

Resolución de ajuste de frecuencia fina

El AD9959 ofrece una resolución de ajuste de 0.12 Hz o mejor, proporcionando un control preciso sobre la frecuencia de las señales que genera.Este nivel de precisión es beneficioso cuando se trabaja en aplicaciones donde los ajustes de pequeñas frecuencia marcan una gran diferencia.

Compensación de fase de alta resolución

Con la resolución de desplazamiento de fase de 14 bits, el AD9959 le permite ajustar la fase de cada canal.Esta característica es útil cuando necesita ajustes de fase exactos entre las señales, como al alinear múltiples señales en sistemas de matriz en fase.

Escala de amplitud de salida

El AD9959 proporciona una resolución de escala de amplitud de salida de 10 bits.Esto le permite ajustar la amplitud de salida con alta precisión, dándole la flexibilidad de controlar la intensidad de la señal con mayor precisión.

Interfaz de puerto de E/S en serie mejorada

La interfaz de puerto de E/S en serie (SPI) ofrece un mejor rendimiento de datos, lo que le permite transferir datos de manera rápida y eficiente entre el dispositivo y su sistema.Esto acelera la comunicación, que puede ser útil en aplicaciones de ritmo rápido.

Control de apagado

El AD9959 incluye opciones de software y hardware para apagar hacia abajo, lo que le brinda control sobre cómo y cuándo ahorrar energía.Esta característica es particularmente útil en diseños conscientes de la energía donde la eficiencia energética es una prioridad.

Operación de suministro dual

El dispositivo funciona con un sistema de suministro dual: 1.8 V para el núcleo DDS y 3.3 V para la E/S en serie.Esta configuración ayuda a equilibrar el rendimiento con las necesidades de energía, lo que lo hace adaptable a varios entornos de diseño.

Sincronización de dispositivos múltiples

El AD9959 admite la sincronización en múltiples dispositivos, lo que le permite expandir su diseño con unidades adicionales mientras mantiene un momento preciso entre ellos.Esto hace que sea más fácil escalar sus proyectos sin perder la sincronización.

Multiplicador de referencia seleccionable

Con un multiplicador de Refclk seleccionable que varía de 4 × a 20 ×, el AD9959 ofrece flexibilidad en las opciones de marcado, lo que le permite elegir la mejor configuración para su diseño.

Oscilador de cristal refclk incorporado

El dispositivo incluye un oscilador de cristal REFCLK incorporado, que simplifica su proceso de diseño al reducir la necesidad de componentes externos, lo que facilita la administración de la sincronización dentro del sistema.

Paquete LFCSP compacto de 56 peces

El AD9959 viene en un paquete LFCSP de 56 líderes, que proporciona una opción compacta y de ahorro de espacio para integrar múltiples canales DDS en su diseño.Este pequeño factor de forma es ideal cuando necesita una alta funcionalidad sin ocupar demasiado espacio de tablero.

Aplicaciones comunes AD9959

Osciladores locales ágiles

El AD9959 es adecuado para su uso en osciladores locales ágiles, proporcionando un control preciso sobre la frecuencia, la fase y la amplitud.Esto lo convierte en una excelente opción cuando necesita una generación de señales flexible y ajustable en sistemas de radio u otros equipos de comunicaciones.

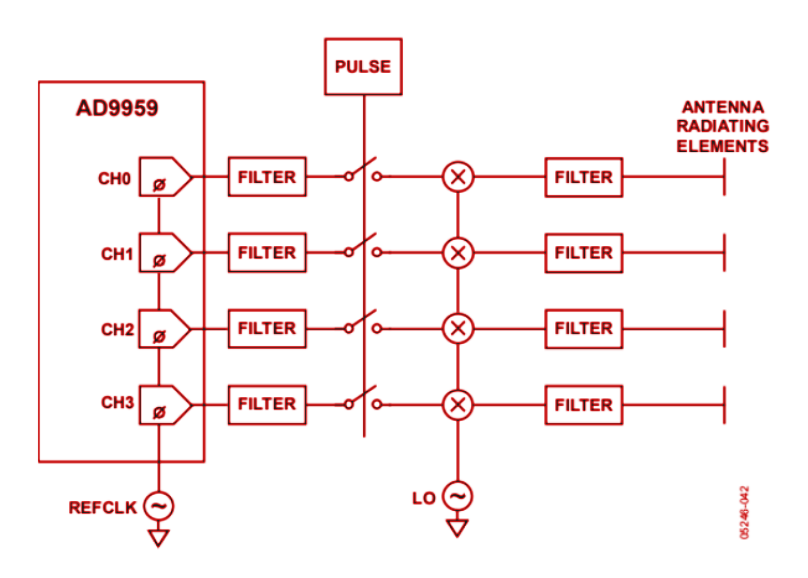

Radares de matriz y sonars por etapas

En los sistemas de radar y sonar de matriz en fase, la sincronización precisa de los canales de señal múltiples es crítica.La capacidad del AD9959 para manejar el control y la sincronización independientes a través de múltiples canales lo convierte en un ajuste perfecto para estas aplicaciones, asegurando un procesamiento y tiempo de señal precisos.

Instrumentación

El AD9959 se puede usar en varios tipos de instrumentación, particularmente en dispositivos que requieren una generación y control de señal precisos.Ya sea para probar, medir o calibrar sistemas, la flexibilidad del dispositivo para ajustar la frecuencia, la fase y la amplitud agrega versatilidad a sus diseños.

Marcado sincronizado

Para los proyectos que necesitan un registro sincronizado a través de múltiples canales, el AD9959 ofrece una excelente solución.Sus características de sincronización incorporadas le permiten mantener el tiempo exacto entre los canales, lo que lo hace ideal para sistemas donde la precisión de la sincronización es crucial.

Fuente de RF para filtros sintonizables acousto-ópticos (AOTF)

El AD9959 puede actuar como una fuente de RF para filtros sintonizables acústicos (AOTF), proporcionando una generación de señal confiable y precisa para estos sistemas ópticos.Su flexibilidad en el control de frecuencia y amplitud le permite satisfacer las demandas de tales aplicaciones especializadas.

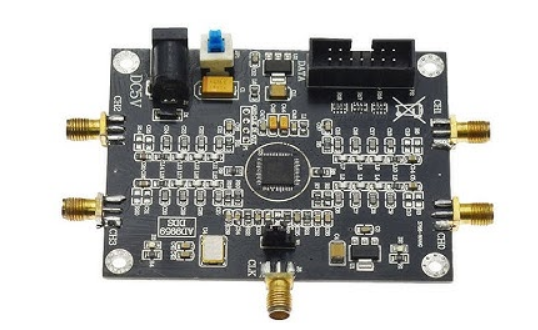

Descripción general del circuito de aplicación AD9959

Diagrama de esquema de dimensión AD9959

AD9959 Información del fabricante

Analog Devices ha sido una empresa líder en la creación de circuitos integrados desde 1965. La compañía se especializa en el diseño y la producción de circuitos que ayudan a convertir, condicionar y procesar señales del mundo real, como la temperatura, el sonido y el movimiento, en señales eléctricas.Estos circuitos se utilizan en una amplia gama de sistemas electrónicos en todo el mundo.

Preguntas frecuentes [Preguntas frecuentes]

1. ¿Para qué se usa el AD9959?

El AD9959 contiene cuatro núcleos de sintetizador digital directo (DDS), cada uno que permite un control independiente de frecuencia, fase y amplitud en su canal respectivo.Esta flexibilidad puede ayudarlo a equilibrar cualquier inconsistencia en las señales causadas por procesos analógicos como filtrado, amplificación o diferencias de diseño en la PCB.

2. ¿Cómo funciona el AD9959?

El AD9959 puede modular la frecuencia, la fase o la amplitud (usando FSK, PSK o Ask Modulation) con hasta 16 niveles distintos.Usted controla esta modulación aplicando señales a los pines de perfil, lo que permite que el chip cambie entre diferentes niveles de modulación según sea necesario.

Acerca de nosotros

ALLELCO LIMITED

Lee mas

Consulta rápida

Envíe una consulta, responderemos de inmediato.

Una guía completa para el convertidor de voltaje TC7660COA

en 24/10/2024

Comprender el transistor TIP120

en 24/10/2024

Publicaciones populares

-

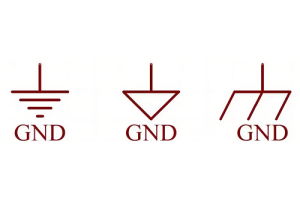

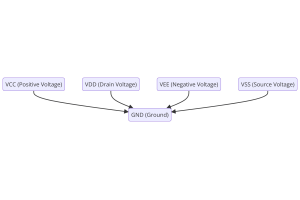

¿Qué es GND en el circuito?

en 01/01/1970 2924

-

Guía del conector RJ-45: códigos de color del conector RJ-45, esquemas de cableado, aplicaciones R-J45, hojas de datos RJ-45

en 01/01/1970 2484

-

Tipos de conector de fibra: SC vs LC y LC vs MTP

en 01/01/1970 2075

-

Comprensión de los voltajes de la fuente de alimentación en Electronics VCC, VDD, VEE, VSS y GND

en 08/11/0400 1863

-

Comparación entre DB9 y RS232

en 01/01/1970 1757

-

¿Qué es una batería LR44?

La electricidad, esa fuerza ubicua, impregna en silencio todos los aspectos de nuestra vida diaria, desde dispositivos triviales hasta equipos médicos potencialmente mortales, juega un papel silencioso.Sin embargo, realmente comprender esta energía, especialmente cómo almacenarla y producirla de manera eficiente, no es una tarea fácil.Es en este fondo que este artículo se centrará en un tipo...en 01/01/1970 1706

-

Comprender los fundamentos: resistencia a la inductancia y capacidad

En la intrincada danza de la ingeniería eléctrica, un trío de elementos fundamentales toma el centro del escenario: inductancia, resistencia y capacitancia.Cada uno tiene rasgos únicos que dictan los ritmos dinámicos de los circuitos electrónicos.Aquí, nos embarcamos en un viaje para descifrar las complejidades de estos componentes, para descubrir sus distintos roles y usos prácticos dentr...en 01/01/1970 1649

-

Guía integral de batería CR2430: especificaciones, aplicaciones y comparación con las baterías CR2032

¿Qué es la batería CR2430?Beneficios de las baterías CR2430NormaAplicaciones de batería CR2430CR2430 equivalenteCR2430 vs CR2032Batería CR2430 TamañoQué buscar al comprar el CR2430 y los equivalentesHoja de datos pdfPreguntas frecuentes Las baterías son el corazón de pequeños dispositivos electrónicos.Entre los muchos tipos disponibles, las células de monedas juegan un papel crucial, ...en 01/01/1970 1536

-

¿Qué es RF y por qué lo usamos?

La tecnología de radiofrecuencia (RF) es una parte clave de la comunicación inalámbrica moderna, lo que permite la transmisión de datos a largas distancias sin conexiones físicas.Este artículo profundiza en los conceptos básicos de RF, explicando cómo la radiación electromagnética (EMR) hace posible la comunicación de RF.Exploraremos los principios de EMR, la creación y el control de l...en 01/01/1970 1528

-

CR2450 vs CR2032: ¿Se puede usar la batería en su lugar?

Las baterías de manganeso de litio tienen algunas similitudes con otras baterías de litio.La alta densidad de energía y la larga vida útil son las características que tienen en común.Este tipo de batería ha ganado la confianza y el favor de muchos consumidores debido a su seguridad única.¿Gadgets tecnológicos caros?¿Pequeños electrodomésticos en nuestros hogares?Mira a tu alrededor y ...en 01/01/1970 1497