Diagrama de pinout y bloque del cable PL-USB2-Blaster

El Blaster PL-USB2 es un componente importante de la serie de cable de descarga FPGA de Intel, que permite la configuración de FPGA Intel® a través de una conexión USB.Este artículo proporciona una visión detallada de su diseño y funcionalidad, incluidos su pinout, características, diagrama de bloques, conexiones y detalles operativos.Nuestro objetivo es explorar no solo los detalles técnicos del dispositivo, sino también la facilidad y efectividad que aporta a las configuraciones FPGA.Catalogar

¿Qué es el blaster PL-USB2?

El PL-USB2-Blaster es un excelente componente en la serie de cable de descarga Intel® FPGA, que facilita la transferencia de datos eficiente entre una computadora y un FPGA a través de una conexión USB.Este cable mejora la prototipos iterativos y la programación de producción al transmitir datos de configuración a través de un encabezado estándar de 10 pines en una placa de circuito.Agarrar las funcionalidades centrales del blaster PL-USB2 se usa para su implementación efectiva en diferentes etapas del desarrollo de FPGA.Este dispositivo garantiza una integración perfecta en diversos entornos de desarrollo, caracterizados por sus capacidades de transmisión de datos rápidas y consistentes.

Durante las etapas de prototipos iterativos, se necesitan precisión y agilidad.El Blaster PL-USB2 admite una carga rápida de configuraciones actualizadas, lo que permite pruebas rápidas y ajustes de configuraciones FPGA.Esta agilidad es beneficiosa en los entornos que requieren iteraciones frecuentes para ajustar los diseños y abordar rápidamente los problemas.Se requiere consistencia en el rendimiento en la programación de producción.El Blaster PL-USB2 garantiza una programación precisa de las configuraciones finales en el FPGA, asegurando la confiabilidad en las aplicaciones de uso final.Esta consistencia ayuda a minimizar las discrepancias y mejora la eficiencia, particularmente cuando se programan grandes volúmenes de unidades.

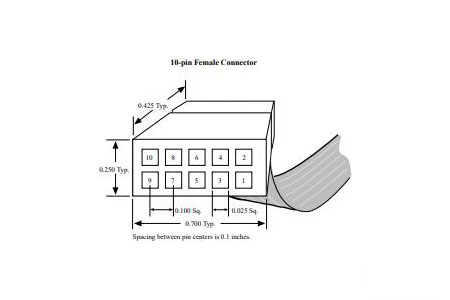

Pinout de PL-USB2-Blaster

|

Número de alfiler |

Nombre |

Descripción de la función |

|

1 |

DCL |

El pin DCL es bueno para propagar la señal del reloj

para operaciones síncronas.Es importante minimizar el ruido y mantener

Conexiones estables similares a las prácticas de diseño de circuitos de alta frecuencia. |

|

2 |

Gnd |

Tierra (GND) sirve como voltaje de referencia, asegurando

Conrazización constante y confiable para prevenir discrepancias en los niveles de señal

y mitigar problemas como bucles de tierra. |

|

3 |

Conf_ |

El pin de conf_done indica la finalización del dispositivo

configuración.Monitorear este pin es utilizar para verificar el exitoso

Inicialización de periféricos. |

|

4 |

VOCC (TRGT) |

El pin de VOCC suministra energía al sistema de destino, con un

Concéntrese en suministrar el voltaje correcto para evitar el voltaje bajo o excesivo

Condiciones, utilizando métodos de regulación de gestión de energía. |

|

5 |

nconfig |

El pin de nconfig facilita la reconfiguración del dispositivo

La activación, garantizar el reinicio o la reprogramación se logra sin

interrupciones. |

|

6 |

NCE |

El PIN de NCE (Chip de chip) controla el estado habilitador de

el dispositivo, que requiere una afirmación adecuada para activar el dispositivo cuando sea necesario,

similar al control de habilitar señales en circuitos integrados. |

|

7 |

Data |

Dataut es responsable de la salida de datos, enfocándose

en la transmisión de señal limpia para proteger la integridad de los datos e incorporar

Protocolos de verificación de errores contra la corrupción de datos. |

|

8 |

NCS |

El pin NCS (Chip Select) activa un dispositivo específico

componentes, con activación controlada y desactivación para garantizar el correcto

Las partes de un dispositivo están activadas en los momentos correctos. |

|

9 |

Asdi |

ASDI se utiliza para los datos de entrada, enfatizando la necesidad de

Entrada de datos precisa y oportuna, sincronización de entrada similar a secuencial

Circuitos lógicos para evitar la falta de comunicación. |

|

10 |

Gnd |

Similar al pin 2, el pin 10 proporciona otra conexión a tierra

punto, centrarse en implementar múltiples puntos de base como estrategia

Común en sistemas de alta precisión para mejorar la estabilidad y el rendimiento. |

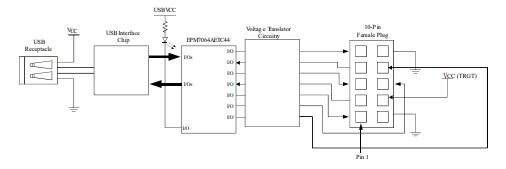

Diagrama funcional PL-USB2-Blaster

Rutas de datos y vías de comunicación

La interfaz de la computadora host sirve como el punto de contacto inicial para los datos de configuración.Actuando como un conducto entre el software de la computadora y el hardware PL-USB2-Blaster, esta interfaz aprovecha los protocolos USB 2.0 de alta velocidad para facilitar la transmisión de datos rápida y confiable.Después de la recepción de datos, la unidad de procesamiento dentro del blaster PL-USB2 asume el control.Esta unidad, que comprende un microcontrolador o FPGA, analiza diligentemente, verifica los errores y los formatos de datos entrantes para garantizar la compatibilidad con los componentes posteriores.

El procesamiento posterior, los datos se alojan temporalmente en unidades de almacenamiento en búfer.Estos búferes manejan las discrepancias de tiempo entre la afluencia de datos de alta velocidad y las velocidades de procesamiento posteriores variables.Se necesitan prácticas efectivas de gestión del búfer, ya que reducen las interrupciones y la pérdida de datos.El siguiente paso implica transmitir los datos bufferados al FPGA a través de una red de enrutamiento claramente definida.Esta red, que involucra multiplexores, demultiplexores y vías dedicadas, está diseñada para preservar la integridad y la sincronización de datos.Una red de enrutamiento bien implementada es importante;El enrutamiento subóptimo puede conducir a errores de configuración y problemas de rendimiento, como se señaló en muchas aplicaciones prácticas.

Control de sincronización y sincronización

Una piedra angular de la arquitectura es el sistema de generación y distribución del reloj, que orquesta el tiempo de transferencia de datos para garantizar una operación perfecta.La precisión en la distribución del reloj a menudo es resaltada por otros como un uso para mantener la sincronización y el rendimiento óptimo.Mantener la integridad de la señal también es un componente clave de la arquitectura del blaster PL-USB2.Se emplean técnicas como señalización diferencial, coincidencia de impedancia y vías blindadas para mitigar la degradación de la señal e interferencia electromagnética (EMI).

Mecanismos de configuración avanzados

El diagrama de arquitectura también representa mecanismos para la detección y corrección de errores.Técnicas como las verificaciones de redundancia cíclica (CRC) y otros algoritmos de detección de errores identifican y corrigen automáticamente las discrepancias del flujo de datos, lo que garantiza la confiabilidad del proceso de configuración.Estos métodos son altamente valorados en numerosas aplicaciones para su papel en el establecimiento de sistemas robustos.Las capacidades de reconfiguración dinámica representan otra característica sofisticada del blaster PL-USB2.Esta funcionalidad permite modificaciones de configuración de FPGA sin detener las operaciones, un rasgo inmensamente valorado en escenarios en los que se requieren adaptabilidad y tiempo de inactividad mínimo.

Usando PL-USB2-Blaster

Instalación del controlador

Inicie el proceso descargando e instalando los controladores proporcionados por Intel.Estos controladores sirven como un puente para la comunicación entre el cable y su dispositivo informático.Encontrará instrucciones completas en el paquete del controlador, que ofrece una guía paso a paso a través de la instalación.

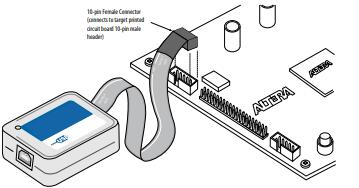

Conexión de hardware

Después de instalar los controladores, vincule el cable PL-USB2-Blaster desde el puerto USB de su computadora al puerto de programación del dispositivo de destino.Esta conexión es buena para preparar los componentes de hardware para la próxima configuración.

Lanzamiento del programador de Quartus Prime

Enciende el software Intel Quartus Prime, dirígete a la herramienta 'Programador' y elige el archivo de configuración de hardware de ajuste.La interfaz amigable del software garantiza un proceso de configuración simple, que permite ajustes y configuraciones rápidas.

Realización de la configuración del dispositivo

Implemente el programador Quartus Prime para ejecutar la configuración del dispositivo.Elija el dispositivo de destino de la lista y cargue los archivos del proyecto relevantes.Inicie la secuencia de programación, y el software administrará la transferencia de datos, configurando efectivamente su dispositivo FPGA.

El papel de Signal Tap

El cable PL-USB2-Blaster extiende el soporte al analizador de lógica de Tap Signal, una herramienta para un análisis lógico riguroso.Signal Tap ofrece un análisis lógico integrado, una característica para depurar y verificar los diseños de FPGA.

Configuración de la señal de toque

Dentro del software Quartus Prime, configure el Analizador Logic Signal Tap para capturar y analizar las señales.Al definir condiciones de activación específicas, puede controlar meticulosamente la recopilación de datos, ayudando a identificar problemas dentro del diseño FPGA.

El uso de Adepto del cable PL-USB2-Blaster exige una comprensión profunda de los reinos de hardware y software.La integración de estas herramientas en el proceso de diseño puede optimizar notablemente los ciclos de desarrollo y mejorar la confiabilidad del producto final.La fusión de la configuración exhaustiva y las capacidades analíticas realmente aumenta la efectividad del desarrollo de FPGA.Se adhiere a estas pautas y aprovechando las características integrales del cable PL-USB2-Blaster y el software Quartus Prime permiten elaborar un flujo de trabajo de desarrollo robusto y eficiente, asegurando un rendimiento superior y la confiabilidad de sus diseños FPGA.

Conexión de cable a tablero

Medidas de seguridad para operación segura

En primer lugar, asegúrese de desconectar todas las fuentes de alimentación antes de comenzar la conexión de cable a tablero.Esta precaución protege contra riesgos eléctricos y salvaguardia los delicados componentes en la placa del dispositivo.

Establecer la conexión

Comience adjuntar el cable de descarga Intel FPGA a la PC.Proceda a conectar el cable al encabezado de 10 pines en la placa del dispositivo.Después de verificar que todas las conexiones son seguras, restaure la fuente de alimentación.Las conexiones seguras pueden evitar errores de datos y facilitar fuertes vías de comunicación entre los dispositivos.

Instalación del controlador

Si el sistema indica la necesidad de una nueva instalación del controlador de hardware, salga del asistente inicial.La adherencia a las pautas de instalación del fabricante asegura que los controladores apropiados estén instalados correctamente.Este enfoque fomenta las capacidades de rendimiento óptimas del dispositivo.La adherencia cuidadosa a las instrucciones de instalación paso a paso de Intel puede evitar instalaciones incompletas que pueden provocar fallas en el sistema.

Separe el cable

Retire la fuente de alimentación antes de desconectar el cable para evitar cualquier posible daño eléctrico.Continúe desconectando el cable de la placa del dispositivo, seguido de desconectarlo de la PC.La secuencia de desconexión adecuada puede mitigar los riesgos vinculados a oleadas de potencia repentina.Después de un proceso de desconexión sistemática, admite la longevidad de los componentes de hardware y puede reducir los gastos de reparación.

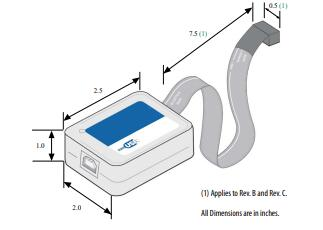

Dimensiones PL-USB2-Blaster

Preguntas frecuentes [Preguntas frecuentes]

1. ¿Cuál es el propósito de un blaster USB?

Un USB Blaster permite a los usuarios de PC programar y configurar dispositivos en el sistema a través de una conexión USB.Esta herramienta optimiza el proceso de desarrollo para usted, lo que lo convierte en un compañero confiable en sus actividades creativas y técnicas.

2. ¿Cómo difiere el blaster USB del USB Blaster II?

El USB Blaster I admite circuitos JTAG entre 2.5V y 3.3V.Por el contrario, el USB Blaster II atiende a un voltaje más amplio de 1.5V a 5V y ofrece características avanzadas.La versatilidad del USB Blaster II permite la compatibilidad con una variedad más amplia de sistemas, ampliando su usabilidad.Esta adaptabilidad mejora su funcionalidad, por lo que es una herramienta muy buscada en escenarios más complejos.

3. ¿Cuáles son los pasos para instalar un controlador USB-Blaster?

En primer lugar, conecte el blaster USB a su PC.Tras la conexión, siga las indicaciones en pantalla que elijan opciones de instalación del controlador.Navegue a los controladores ubicados en el directorio de instalación de Quartus Prime y continúe con el asistente de instalación hasta que el proceso esté completamente completado.Este método directo garantiza una integración perfecta con su entorno de desarrollo.La facilidad de este proceso le permite centrarse más en la innovación y la creatividad.

4. ¿Qué requisitos previos son necesarios para usar el cable de descarga Intel FPGA?

Comience instalando los controladores apropiados en su sistema.Este paso inicial es importante.Posteriormente, configure el hardware a través del software Intel Quartus® Prime.Esta preparación ajusta su configuración para un rendimiento y eficiencia óptimos.

5. ¿Qué recomienda Intel para un uso óptimo del cable de descarga Intel FPGA?

Intel aconseja encarecidamente el uso de la versión más reciente del software Quartus Prime.Al mantenerse actualizados con las últimas iteraciones, otros obtienen acceso a características mejoradas y un rendimiento mejorado.Esta práctica garantiza una más simplificada y haciendo que cada interacción con la herramienta sea más productiva.