# STM32WB55Cx STM32WB55Rx STM32WB55Vx STM32WB35Cx

Errata sheet

# STM32WB55xx/STM32WB35Cx device errata

# Applicability

This document applies to the part numbers of STM32WB55xx/STM32WB35Cx devices and the device variants as stated in this page.

It gives a summary and a description of the device errata, with respect to the device datasheet and reference manual RM0434. Deviation of the real device behavior from the intended device behavior is considered to be a device limitation. Deviation of the description in the reference manual or the datasheet from the intended device behavior is considered to be a documentation erratum. The term *"errata"* applies both to limitations and documentation errata.

# Table 1. Device summary

| Reference   | Part numbers                          |

|-------------|---------------------------------------|

| STM32WB55Cx | STM32WB55CC, STM32WB55CE, STM32WB55CG |

| STM32WB55Rx | STM32WB55RC, STM32WB55RE, STM32WB55RG |

| STM32WB55Vx | STM32WB55VC, STM32WB55VE, STM32WB55VG |

| STM32WB35Cx | STM32WB35CC, STM32WB35CE              |

# Table 2. Device variants

| Reference           | Silicon revision codes        |                       |  |  |

|---------------------|-------------------------------|-----------------------|--|--|

| Reference           | Device marking <sup>(1)</sup> | REV_ID <sup>(2)</sup> |  |  |

| STM32WB55Cx/Rx/Vx   | Y                             | 0x2001                |  |  |

| STIVI32WD33CX/RX/VX | Х                             | 0x2003                |  |  |

| STM32WB35Cx         | A                             | 0x2001                |  |  |

| 31103270B33CX       | X                             | 0x2003                |  |  |

1. Refer to the device datasheet for how to identify this code on different types of package.

2. REV\_ID[15:0] bitfield of DBGMCU\_IDCODE register.

# 1 Summary of device errata

The following table gives a quick reference to the STM32WB55xx/STM32WB35Cx device limitations and their status:

- A = limitation present, workaround available

- N = limitation present, no workaround available

- P = limitation present, partial workaround available

"-" = limitation absent

Applicability of a workaround may depend on specific conditions of target application. Adoption of a workaround may cause restrictions to target application. Workaround for a limitation is deemed partial if it only reduces the rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on the device or in only a subset of operating modes, of the function concerned.

|          |         |                                                                                              |                          | Sta                      | tus                |                    |

|----------|---------|----------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------|--------------------|

| Function | Section | Limitation                                                                                   | STM32WB55Cx/Rx/Vx Rev. Y | STM32WB55Cx/Rx/Vx Rev. X | STM32WB35Cx Rev. A | STM32WB35Cx Rev. X |

|          | 2.1.1   | Interrupted loads to SP can cause erroneous behavior                                         | А                        | Α                        | А                  | А                  |

| Core     | 2.1.2   | VDIV or VSQRT instructions might not complete correctly when very short ISRs are used        | A                        | А                        | A                  | А                  |

|          | 2.1.3   | Store immediate overlapping exception return operation might vector to incorrect interrupt   | А                        | А                        | А                  | А                  |

|          | 2.2.1   | LSI2 not usable as RF low-power clock                                                        | А                        | А                        | А                  | А                  |

|          | 2.2.2   | Unstable LSI1 when it clocks RTC or CSS on LSE                                               | Р                        | Р                        | Р                  | Р                  |

|          | 2.2.3   | Internal voltage reference corrupted upon Stop mode entry with temperature sensing enabled   | А                        | А                        | А                  | А                  |

|          | 2.2.4   | Full JTAG configuration without NJTRST pin cannot be used                                    | А                        | А                        | А                  | Α                  |

|          | 2.2.5   | Auto-incrementing feature of the debug port cannot span more than 1 Kbyte                    | А                        | А                        | А                  | А                  |

|          | 2.2.6   | PC13 signal transitions disturb LSE                                                          | Ν                        | N                        | -                  | -                  |

| System   | 2.2.7   | Wrong DMAMUX synchronization and trigger input connections to EXTI                           | А                        | А                        | А                  | А                  |

|          | 2.2.8   | Incomplete Stop 2 mode entry after a wakeup from debug upon EXTI line 48 event               | A                        | А                        | A                  | А                  |

|          | 2.2.9   | Flash OPTVERR flag is always set after system reset                                          | А                        | А                        | А                  | А                  |

|          | 2.2.10  | Overwriting with all zeros a flash memory location previously programmed with all ones fails | Ν                        | Ν                        | N                  | Ν                  |

|          | 2.2.11  | WLCSP100 RF BLE overconsumption                                                              | Ν                        | N                        | -                  | -                  |

|          | 2.2.12  | WLCSP100 noise coupling in LDO configuration at specific conditions                          | Ρ                        | Ρ                        | -                  | -                  |

# Table 3. Summary of device limitations

# STM32WB55Cx STM32WB55Rx STM32WB55Vx STM32WB35Cx Summary of device errata

|              |         |                                                                                                                 |                          | Sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | itus               |                    |

|--------------|---------|-----------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|

| Function     | Section | Limitation                                                                                                      | STM32WB55Cx/Rx/Vx Rev. Y | STM32WB55Cx/Rx/Vx Rev. X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | STM32WB35Cx Rev. A | STM32WB35Cx Rev. X |

|              | 2.2.13  | FLASH_ECCR corrupted upon reset or power-down occurring<br>during flash memory program or erase operation       | A                        | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                  | А                  |

|              | 2.2.14  | A system reset occurs when nRST_SHDW is set and nRST_STDBY is cleared and Shutdown mode is entered              | А                        | A       A         A       A         A       A         N       N         A       A         N       N         A       A         N       N         A       A         N       N         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A       A         A | А                  | А                  |

|              | 2.2.15  | PH3 signal transitions disturb LSE                                                                              | Ν                        | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                  | N                  |

|              | 2.2.16  | WLCSP100 PA2 signal transitions disturb LSE                                                                     | Ν                        | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                  | -                  |

|              | 2.2.17  | Incorrect exit from Stop modes when the DBGMCU/DBG_STOP is enabled                                              | А                        | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                  | А                  |

|              | 2.2.18  | HSE is switched on immediately on Stop 2 exit, causing an undesired over-consumption                            |                          | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                  | N                  |

|              | 2.2.19  | When $V_{DD}$ exceeds 2.5V in LDO configuration a glitch on HSE may create a hard fault on M4/M0                | А                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                  | -                  |

| System       | 2.2.20  | On WLCSP100 devices, when SMPS is in bypass mode, a glitch on HSE may create a hard fault on M4/M0              | N                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                  | -                  |

|              | 2.2.21  | SMPS functional only with Stop 0 mode and Run mode                                                              | А                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>- A            | -                  |

|              | 2.2.22  | System reset fails to initialize SRAM2 parity if SRAM2_RST is set                                               | А                        | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Α                  | Α                  |

|              | 2.2.23  | SRAM2 content lost upon wakeup from Standby if SRAM2_RST is set                                                 | N                        | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                  | N                  |

|              | 2.2.24  | SMPS current surge upon mode change                                                                             | А                        | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Α                  | Α                  |

|              | 2.2.25  | With HSEGMC greater than 3, the HSE accuracy may not fulfill RF requirements                                    | А                        | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                  | А                  |

|              | 2.2.26  | Corrupted content of the backup domain due to a missed power-<br>on reset after this domain supply voltage drop | А                        | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                  | А                  |

|              | 2.2.27  | Overconsumption in Shutdown mode under specific conditions                                                      | А                        | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Α                  | А                  |

|              | 2.2.28  | Excessive current on $V_{DDA}$ or $V_{DD}$ when $V_{DD}$ level is different from $V_{DDA}$ level                | A                        | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A                  | A                  |

| Radio system | 2.3.1   | RF system wake-up clock set to HSE/1024 cannot be changed                                                       | А                        | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Α                  | Α                  |

| DMA          | 2.4.1   | DMA disable failure and error flag omission upon simultaneous transfer error and global flag clear              | А                        | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                  | A                  |

|              | 2.5.1   | SOFx not asserted when writing into DMAMUX_CFR register                                                         | Ν                        | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                  | N                  |

| DNAANALIY    | 2.5.2   | OFx not asserted for trigger event coinciding with last DMAMUX request                                          | N                        | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                  | N                  |

| DMAMUX       | 2.5.3   | OFx not asserted when writing into DMAMUX_RGCFR register                                                        | Ν                        | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                  | N                  |

|              | 2.5.4   | Wrong input DMA request routed upon specific DMAMUX_CxCR register write coinciding with synchronization event   | А                        | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                  | A                  |

| QUADSPI      | 2.6.1   | First nibble of data not written after dummy phase                                                              | А                        | Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Α                  | Α                  |

# STM32WB55Cx STM32WB55Rx STM32WB55Vx STM32WB35Cx Summary of device errata

|                 |                                                                                                                                                            |                                                                                                         |                          | StatusStatusRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRR </th <th></th> |                    |                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|

| Function        | Section                                                                                                                                                    | Limitation                                                                                              | STM32WB55Cx/Rx/Vx Rev. Y | STM32WB55Cx/Rx/Vx Rev. X                                                                                                                                                           | STM32WB35Cx Rev. A | STM32WB35Cx Rev. X |

|                 | 2.6.2                                                                                                                                                      | Wrong data from memory-mapped read after an indirect mode operation                                     | А                        | А                                                                                                                                                                                  | А                  | A                  |

| QUADSPI         | 2.6.3                                                                                                                                                      | Memory-mapped read operations may fail when timeout counter is enabled                                  | Р                        | Ρ                                                                                                                                                                                  | Ρ                  | Р                  |

|                 | 2.6.4     Memory-mapped access in indirect mode clearing QUADSPI_AR register       2.7.1     Wrong ADC result if conversion done late after calibration or |                                                                                                         | Ρ                        | Ρ                                                                                                                                                                                  | Ρ                  | Р                  |

| 450             | 2.7.1                                                                                                                                                      | Wrong ADC result if conversion done late after calibration or previous conversion                       | A A A                    |                                                                                                                                                                                    | А                  | А                  |

| ADC             | 2.7.2                                                                                                                                                      | Selected external ADC inputs unduly clamped to V <sub>DD</sub> when all analog peripherals are disabled |                          |                                                                                                                                                                                    | А                  |                    |

| VREFBUF         | 2.8.1                                                                                                                                                      | Incorrect voltage reference output values                                                               |                          |                                                                                                                                                                                    |                    | -                  |

| TSC             | 2.9.1                                                                                                                                                      | TSC signal-to-noise concern under specific conditions                                                   | Α                        |                                                                                                                                                                                    |                    |                    |

|                 | 2.10.1                                                                                                                                                     | One-pulse mode trigger not detected in master-slave reset + trigger configuration                       | Р                        | Р                                                                                                                                                                                  | Р                  | Р                  |

| TIM             | 2.10.2                                                                                                                                                     | Consecutive compare event missed in specific conditions                                                 | Ν                        | Ν                                                                                                                                                                                  | Ν                  | N                  |

|                 | 2.10.3                                                                                                                                                     | Output compare clear not working with external counter reset                                            | Р                        | Р                                                                                                                                                                                  | Р                  | Р                  |

|                 | 2.11.1                                                                                                                                                     | Device may remain stuck in LPTIM interrupt when entering Stop mode                                      | А                        | A                                                                                                                                                                                  | А                  | A                  |

| LPTIM           | 2.11.2                                                                                                                                                     | Device may remain stuck in LPTIM interrupt when clearing event flag                                     | Р                        | Р                                                                                                                                                                                  | Р                  | Р                  |

|                 | 2.11.3                                                                                                                                                     | LPTIM events and PWM output are delayed by one kernel clock cycle                                       | Р                        | Р                                                                                                                                                                                  | Р                  | Р                  |

|                 | 2.11.4                                                                                                                                                     | LPTIM clocked by LSI2 also requires LSI1                                                                | А                        | А                                                                                                                                                                                  | А                  | А                  |

|                 | 2.12.1                                                                                                                                                     | RTC interrupt can be masked by another RTC interrupt                                                    | А                        | А                                                                                                                                                                                  | А                  | А                  |

| RTC and<br>TAMP | 2.12.2                                                                                                                                                     | Calendar initialization may fail in case of consecutive INIT mode entry                                 | А                        | A                                                                                                                                                                                  | А                  | А                  |

|                 | 2.12.3                                                                                                                                                     | Alarm flag may be repeatedly set when the core is stopped in debug                                      | N                        | N                                                                                                                                                                                  | N                  | N                  |

|                 | 2.13.1                                                                                                                                                     | Wrong data sampling when data setup time ( $t_{SU;DAT}$ ) is shorter than one I2C kernel clock period   | Р                        | Р                                                                                                                                                                                  | Р                  | Р                  |

|                 | 2.13.2                                                                                                                                                     | Spurious bus error detection in master mode                                                             | А                        | Α                                                                                                                                                                                  | А                  | А                  |

| I2C             | 2.13.3                                                                                                                                                     | Spurious master transfer upon own slave address match                                                   | Р                        | Р                                                                                                                                                                                  | Р                  | Р                  |

|                 | 2.13.5                                                                                                                                                     | OVR flag not set in underrun condition                                                                  | N                        | N                                                                                                                                                                                  | N                  | N                  |

|                 | 2.13.6                                                                                                                                                     | Transmission stalled after first byte transfer                                                          | А                        | А                                                                                                                                                                                  | А                  | А                  |

| USART           | 2.14.1                                                                                                                                                     | Anticipated end-of-transmission signaling in SPI slave mode                                             | Α                        | Α                                                                                                                                                                                  | Α                  | Α                  |

|                 | 2.14.2                                                                                                                                                     | Data corruption due to noisy receive line                                                               | Ν                        | Ν                                                                                                                                                                                  | Ν                  | Ν                  |

# STM32WB55Cx STM32WB55Rx STM32WB55Vx STM32WB35Cx Summary of device errata

|          |         |                                                                                       |                          |                          | Status             |                    |  |  |

|----------|---------|---------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------|--------------------|--|--|

| Function | Section | Limitation                                                                            | STM32WB55Cx/Rx/Vx Rev. Y | STM32WB55Cx/Rx/Vx Rev. X | STM32WB35Cx Rev. A | STM32WB35Cx Rev. X |  |  |

| LPUART   | 2.15.1  | Possible LPUART transmitter issue when using low BRR[15:0] value                      | Ρ                        | Ρ                        | Ρ                  | Р                  |  |  |

|          | 2.16.1  | BSY bit may stay high when SPI is disabled                                            | А                        | А                        | Α                  | Α                  |  |  |

| SPI      | 2.16.2  | BSY bit may stay high at the end of data transfer in slave mode                       | А                        | Α                        | Α                  | Α                  |  |  |

|          | 2.16.3  | Wrong CRC in full-duplex mode handled by DMA with imbalanced setting of data counters | А                        | А                        | А                  | А                  |  |  |

|          | 2.17.2  | ESOF interrupt timing desynchronized after resume signaling                           | А                        | Α                        | А                  | А                  |  |  |

| USB      | 2.17.3  | Incorrect CRC16 in the memory buffer                                                  | Ν                        | N                        | N                  | N                  |  |  |

|          | 2.17.4  | Device not responding to USB messages to its endpoint 0xF                             | Ν                        | N                        | N                  | N                  |  |  |

The following table gives a quick reference to the documentation errata.

# Table 4. Summary of device documentation errata

| Function | Section | Documentation erratum                                            |

|----------|---------|------------------------------------------------------------------|

| I2C      | 2.13.4  | START bit is cleared upon setting ADDRCF, not upon address match |

| USB      | 2.17.1  | Possible packet memory overrun/underrun at low APB frequency     |

# 2 Description of device errata

The following sections describe the errata of the applicable devices with Arm<sup>®</sup> core and provide workarounds if available. They are grouped by device functions.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

# arm

# 2.1 Core

Reference manual and errata notice for the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 FPU core revision r0p1 is available from http:// infocenter.arm.com. Only applicable information from the Arm errata notice is replicated in this document.

# 2.1.1 Interrupted loads to SP can cause erroneous behavior

This limitation is registered under Arm ID number 752770 and classified into "Category B". Its impact to the device is minor.

# Description

If an interrupt occurs during the data-phase of a single word load to the stack-pointer (SP/R13), erroneous behavior can occur. In all cases, returning from the interrupt will result in the load instruction being executed an additional time. For all instructions performing an update to the base register, the base register will be erroneously updated on each execution, resulting in the stack-pointer being loaded from an incorrect memory location.

The affected instructions that can result in the load transaction being repeated are:

- LDR SP, [Rn],#imm

- LDR SP, [Rn,#imm]!

- LDR SP, [Rn,#imm]

- LDR SP, [Rn]

- LDR SP, [Rn,Rm]

The affected instructions that can result in the stack-pointer being loaded from an incorrect memory address are:

- LDR SP,[Rn],#imm

- LDR SP,[Rn,#imm]!

As compilers do not generate these particular instructions, the limitation is only likely to occur with hand-written assembly code.

#### Workaround

Both issues may be worked around by replacing the direct load to the stack-pointer, with an intermediate load to a general-purpose register followed by a move to the stack-pointer.

# 2.1.2 VDIV or VSQRT instructions might not complete correctly when very short ISRs are used

This limitation is registered under Arm ID number 776924 and classified into "Category B". Its impact to the device is limited.

#### Description

The VDIV and VSQRT instructions take 14 cycles to execute. When an interrupt is taken a VDIV or VSQRT instruction is not terminated, and completes its execution while the interrupt stacking occurs. If lazy context save of floating point state is enabled then the automatic stacking of the floating point context does not occur until a floating point instruction is executed inside the interrupt service routine.

Lazy context save is enabled by default. When it is enabled, the minimum time for the first instruction in the interrupt service routine to start executing is 12 cycles. In certain timing conditions, and if there is only one or two instructions inside the interrupt service routine, then the VDIV or VSQRT instruction might not write its result to the register bank or to the FPSCR.

The failure occurs when the following condition is met:

- 1. The floating point unit is enabled

- 2. Lazy context saving is not disabled

- 3. A VDIV or VSQRT is executed

- 4. The destination register for the VDIV or VSQRT is one of s0 - s15

- 5 An interrupt occurs and is taken

- 6. The interrupt service routine being executed does not contain a floating point instruction

- 7. Within 14 cycles after the VDIV or VSQRT is executed, an interrupt return is executed

A minimum of 12 of these 14 cycles are utilized for the context state stacking, which leaves 2 cycles for instructions inside the interrupt service routine, or 2 wait states applied to the entire stacking sequence (which means that it is not a constant wait state for every access).

In general, this means that if the memory system inserts wait states for stack transactions (that is, external memory is used for stack data), then this erratum cannot be observed.

The effect of this erratum is that the VDIV or VQSRT instruction does not complete correctly and the register bank and FPSCR are not updated, which means that these registers hold incorrect, out of date, data.

# Workaround

A workaround is only required if the floating point unit is enabled. A workaround is not required if the stack is in external memory.

There are two possible workarounds:

- Disable lazy context save of floating point state by clearing LSPEN to 0 (bit 30 of the FPCCR at address 0xE000EF34).

- Ensure that every interrupt service routine contains more than 2 instructions in addition to the exception return instruction.

#### 2.1.3 Store immediate overlapping exception return operation might vector to incorrect interrupt

This limitation is registered under Arm ID number 838869 and classified into "Category B (rare)". Its impact to the device is minor.

# Description

The core includes a write buffer that permits execution to continue while a store is waiting on the bus. Under specific timing conditions, during an exception return while this buffer is still in use by a store instruction, a late change in selection of the next interrupt to be taken might result in there being a mismatch between the interrupt acknowledged by the interrupt controller and the vector fetched by the processor.

The failure occurs when the following condition is met:

1. The handler for interrupt A is being executed.

- 2. Interrupt B, of the same or lower priority than interrupt A, is pending.

- 3 A store with immediate offset instruction is executed to a bufferable location.

- STR/STRH/STRB <Rt>, [<Rn>,#imm] \_

- STR/STRH/STRB <Rt>, [<Rn>,#imm]!

- STR/STRH/STRB <Rt>, [<Rn>],#imm

- 4. Any number of additional data-processing instructions can be executed.

- 5 A BX instruction is executed that causes an exception return.

- The store data has wait states applied to it such that the data is accepted at least two cycles after the BX is 6. executed.

- Minimally, this is two cycles if the store and the BX instruction have no additional instructions between them.

- The number of wait states required to observe this erratum needs to be increased by the number of cycles between the store and the interrupt service routine exit instruction.

- Before the bus accepts the buffered store data, another interrupt C is asserted which has the same or 7. lower priority as A, but a greater priority than B.

# Example:

The processor should execute interrupt handler C, and on completion of handler C should execute the handler for B. If the conditions above are met, then this erratum results in the processor erroneously clearing the pending state of interrupt C, and then executing the handler for B twice. The first time the handler for B is executed it will be at interrupt C's priority level. If interrupt C is pended by a level-based interrupt which is cleared by C's handler then interrupt C will be pended again once the handler for B has completed and the handler for C will be executed.

As the STM32 interrupt C is level based, it eventually becomes pending again and is subsequently handled.

#### Workaround

For software not using the memory protection unit, this erratum can be worked around by setting DISDEFWBUF in the Auxiliary Control Register.

In all other cases, the erratum can be avoided by ensuring a DSB occurs between the store and the BX instruction. For exception handlers written in C, this can be achieved by inserting the appropriate set of intrinsics or inline assembly just before the end of the interrupt function, for example:

# ARMCC:

```

...

__schedule_barrier();

__asm{DSB};

__schedule_barrier();

}

```

#### GCC:

```

...

_asm volatile ("dsb 0xf":::"memory");

}

```

# 2.2 System

#### 2.2.1 LSI2 not usable as RF low-power clock

#### Description

The calibration mechanism and jitter peaks cause the LSI2 clock to exceed the maximum 500 ppm frequency deviation specified in the Bluetooth<sup>®</sup> Low Energy standard for low-speed clock.

#### Workaround

Clock the Bluetooth® peripheral using the LSE oscillator, instead of the LSI2.

#### 2.2.2 Unstable LSI1 when it clocks RTC or CSS on LSE

#### Description

The LSI1 clock can become unstable (duty cycle different from 50 %) and its maximum frequency can become significantly higher than 32 kHz, when:

- LSI1 clocks the RTC, or it clocks the clock security system (CSS) on LSE (which holds when the LSECSSON bit set), and

- the V<sub>DD</sub> power domain is reset while the backup domain is not reset, which happens:

- upon exiting Shutdown mode

- if V<sub>BAT</sub> is separate from V<sub>DD</sub> and V<sub>DD</sub> goes off then on

- if V<sub>BAT</sub> is tied to V<sub>DD</sub> (internally in the package for products not featuring the VBAT pin, or externally) and a short (< 1 ms) V<sub>DD</sub> drop under V<sub>DD</sub>(min) occurs

Apply one of the following measures:

- Clock the RTC with LSE or HSE/32, without using the CSS on LSE

- If LSI1 clocks the RTC or when the LSECSSON bit is set, reset the backup domain upon each V<sub>DD</sub> power up (when the BORRSTF flag is set). If V<sub>BAT</sub> is separate from V<sub>DD</sub>, also restore the RTC configuration, backup registers and anti-tampering configuration.

# 2.2.3 Internal voltage reference corrupted upon Stop mode entry with temperature sensing enabled

# Description

When entering Stop mode with the temperature sensor channel and the associated ADC(s) enabled, the internal voltage reference may be corrupted.

The occurrence of the corruption depends on the supply voltage and the temperature.

The corruption of the internal voltage reference may cause:

- an overvoltage in V<sub>CORE</sub> domain

- an overshoot / undershoot of internal clock (LSI, HSI, MSI) frequencies

- a spurious brown-out reset

The limitation applies to Stop 1 and Stop 2 modes.

## Workaround

Before entering Stop mode:

- Disable the ADC(s) using the temperature sensor signal as input, and/or

- Disable the temperature sensor channel, by clearing the CH17SEL bit of the ADCx\_CCR register.

Disabling both the ADC(s) and the temperature sensor channel reduces the power consumption during Stop mode.

# 2.2.4 Full JTAG configuration without NJTRST pin cannot be used

#### Description

When using the JTAG debug port in Debug mode, the connection with the debugger is lost if the NJTRST pin (PB4) is used as a GPIO or for an alternate function other than NJTRST. Only the 4-wire JTAG port configuration is impacted.

#### Workaround

Use the SWD debug port instead of the full 4-wire JTAG port.

#### 2.2.5 Auto-incrementing feature of the debug port cannot span more than 1 Kbyte

#### Description

The address auto-increment function of the AP2/AHB access ports is limited to 1 Kbyte of contiguous data.

#### Workaround

To write a contiguous chunk of data larger than 1 Kbyte to an AP2/AHB access port, split and write it in blocks not exceeding 1 Kbyte each.

# 2.2.6 PC13 signal transitions disturb LSE

#### Description

The PC13 port toggling disturbs the LSE clock. It may not be usable when LSE is used.

None.

# 2.2.7 Wrong DMAMUX synchronization and trigger input connections to EXTI

#### Description

By error, synchronization and trigger inputs of the DMAMUX peripheral are connected to interrupt output lines of the EXTI block, instead of being connected to its SYSCFG multiplexer output lines.

The EXTI interrupt lines exhibit a rising-edge transition upon each active transition (rising, falling or both) of corresponding GPIOs, as defined in the EXTI\_RTSRx and EXTI\_FTSRx registers.

As a consequence, the falling active edge option of the DMAMUX synchronization and trigger inputs is unusable because falling edges on these inputs do not occur upon GPIO events but upon clearing the EXTI interrupt pending flags (by setting the corresponding PIF bits of the EXTI\_PRx register).

#### Workaround

For the DMAMUX synchronization and trigger events to occur upon determined rising or/and falling edge of the corresponding GPIOs:

- Set the desired active edge polarities of the corresponding GPIOs through the EXTI\_RTSRx and EXTI\_FTSRx registers.

- Set the active edge polarity to rising for all corresponding DMAMUX input lines, through the SPOL bits

of the DMAMUX\_CxCR register (for synchronization inputs) and the GPOL bits of the DMAMUX\_RGxCR

register (for trigger inputs).

- Ensure that EXTI interrupt pending flags corresponding to the GPIOs used for DMAMUX inputs are cleared in the EXTI interrupt service routine.

*Note:* This can be ensured if using the *HAL\_GPIO\_IrqHandler* function provided by STMicroelectronics.

#### 2.2.8 Incomplete Stop 2 mode entry after a wakeup from debug upon EXTI line 48 event

#### Description

With the JTAG debugger enabled on GPIO pins and after a wakeup from debug triggered by an event on EXTI line 48 (CDBGPWRUPREQ), the device may enter in a state in which attempts to enter Stop 2 mode are not fully effective: The CPUs duly enter their respective CStop modes and are able to wake up so the software execution is not disturbed. However, the system does not transit to a low-power state and thus keeps a power consumption higher than expected.

#### Workaround

Before entering Stop 2 mode, mask *wakeup with interrupt request* from EXTI line 48 (CDBGPWRUPREQ) in both EXTI\_IMR2 and EXTI\_C2IMR2 registers.

# 2.2.9 Flash OPTVERR flag is always set after system reset

#### Description

During option byte loading, the options are read by double word with ECC. If the word and its complement are not matching, the OPTVERR flag is set.

However, the OPTVERR flag is always set after a system reset despite all option bytes being loaded and read correctly.

# Workaround

After reset, clear the OPTVERR flag in FLASH\_SR register.

# 2.2.10 Overwriting with all zeros a flash memory location previously programmed with all ones fails

# Description

Any attempt to re-program with all zeros (0x0000 0000 0000 0000) a flash memory location previously programmed with 0xFFFF FFFF FFFF FFFF fails and the PROGERR flag of the FLASH\_SR register is set.

Note: Flash memory locations in the erased state (that is, not programmed) are not affected by this failure. They can be programmed with any value.

#### Workaround

None.

#### 2.2.11 WLCSP100 RF BLE overconsumption

#### Description

For BLE operation, the device housed in WLCSP100 package requires a specific software management that leads to RX and TX overconsumption. The following table shows the impacted parameters:

| Symbol              | Parameter                     | Conditions                  | Тур | Unit |

|---------------------|-------------------------------|-----------------------------|-----|------|

|                     |                               | SMPS bypass                 | 14  |      |

| I <sub>txmax</sub>  | TX maximum output consumption | SMPS on                     | 8.4 |      |

|                     |                               | V <sub>FBSMPS</sub> = 1.7 V | 0.4 |      |

|                     | TX 0 dBm output consumption   | SMPS bypass                 | 9.4 |      |

| I <sub>tx0dbm</sub> |                               | SMPS on                     | 5.5 | mA   |

|                     |                               | V <sub>FBSMPS</sub> = 1.4 V | 5.5 |      |

|                     |                               | SMPS bypass                 | 8.6 |      |

| I <sub>rxlo</sub>   |                               | SMPS on                     | 4.9 |      |

|                     |                               | V <sub>FBSMPS</sub> = 1.4 V | 4.9 |      |

#### Workaround

None.

# 2.2.12 WLCSP100 noise coupling in LDO configuration at specific conditions

#### Description

In LDO configuration of WLCSP100 device, noise on power supply lines may negatively impact the RF (BLE and 802.15.4) interoperability when the die temperature is -20 °C or less while the  $V_{DD}$  supply voltage is 3.3 V or more.

Note: The SMPS configuration is exempt of the issue described.

#### Workaround

If the combination of low die temperature and high V<sub>DD</sub> as indicated cannot be avoided, use SMPS configuration.

# 2.2.13 FLASH\_ECCR corrupted upon reset or power-down occurring during flash memory program or erase operation

#### Description

Reset or power-down occurring during a flash memory location program or erase operation, followed by a read of the same memory location, may lead to a corruption of the FLASH\_ECCR register content.

Under such condition, erase the page(s) corresponding to the flash memory location.

# 2.2.14 A system reset occurs when nRST\_SHDW is set and nRST\_STDBY is cleared and Shutdown mode is entered

#### Description

When the following configuration is selected:

- nRST\_SHDW is set

- nRST\_STDBY is cleared,

a system reset is generated when Shutdown mode is entered.

# Workaround

The only valid configuration to avoid a reset after entering into Shutdown mode is the following:

- nRST\_SHDW is set

- nRST\_STDBY is set.

# 2.2.15 PH3 signal transitions disturb LSE

#### Description

Toggling on the PH3 port disturbs the LSE clock. The PH3 port may not be usable at the same time as LSE is used.

#### Workaround

None

# 2.2.16 WLCSP100 PA2 signal transitions disturb LSE

#### Description

Toggling on the PA2 port disturbs the LSE clock. The PA2 port may not be usable at the same time as LSE is used. This limitation concerns the WLCSP100 package.

#### Workaround

None.

# 2.2.17 Incorrect exit from Stop modes when the DBGMCU/DBG\_STOP is enabled

#### Description

When DBG\_STOP is set in the microcontroller debug unit (DBGMCU), systick is still running and can trigger the CPU to exit Stop 0, Stop 1, or Stop 2, but the system remains in low power state. The CPU therefore fetches incorrect data from the inactive Flash which will generate a hard fault.

#### Workaround

Disable systick before entering in Stop mode when DBG\_STOP is set in DBGMCU.

# **2.2.18** HSE is switched on immediately on Stop 2 exit, causing an undesired over-consumption

# Description

An internal undefined value present on the RCC HSE input may trigger HSE to restart immediately when Stop 2 condition ends.

# Workaround

None

# 2.2.19 When V<sub>DD</sub> exceeds 2.5V in LDO configuration a glitch on HSE may create a hard fault on M4/M0

#### Description

When RF activity starts, the internal RF LDOs switches on at the same time and produces an extra HSE clock cycle pulse.

The CPUs process wrong data and Bluetooth<sup>®</sup> Low Energy firmware becomes unstable.

The Hard Fault can be observed in case SYSCLK=HSE. Otherwise the risk is radio malfunction since clocked from HSE directly too.

#### Workaround

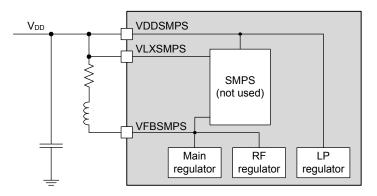

Add a series inductance and resistor between VLXSMPS and VFBSMPS pins as illustrated in the figure.

The recommended inductor characteristics are the inductance 1.8 nH +/- 0.1 nH, self-resonance frequency of 6 Ghz +/-15 %, and rated current of 1000 mA. The resistor of 2.2  $\Omega$  recommended resistance must be dimensioned to dissipate 1 watt during 5 ns. Refer to Minimal BOM for STM32WB Series microcontrollers (AN5290) for more details.

#### Figure 1. Workaround

# 2.2.20 On WLCSP100 devices, when SMPS is in bypass mode, a glitch on HSE may create a hard fault on M4/M0

# Description

When RF activity starts, the internal RF LDO switches on at the same time and produces an extra HSE clock cycle pulse.

The CPUs process wrong data and Bluetooth<sup>®</sup> Low Energy firmware becomes unstable. The issue occurs on the devices housed in the WLCSP100 package.

#### Workaround

None.

# 2.2.21 SMPS functional only with Stop 0 mode and Run mode

#### Description

In Stop 2 mode and Stop 1 mode, during the switching between SMPS and SMPS bypass modes, the SMPS may generate an unstable situation that may cause interruption of the full system.

#### Workaround

Use SMPS with Stop 0 mode without switching between bypass and ON, or use the LDO configuration.

#### 2.2.22 System reset fails to initialize SRAM2 parity if SRAM2\_RST is set

#### Description

With the SRAM2\_RST and SRAM2\_PE bits set, the hardware does not correctly initialize the parity upon the system reset. As a consequence, read accesses to SRAM2 locations not previously written by the CPU trigger an NMI due to failing parity check.

#### Workaround

When enabling the SRAM2 parity by setting the SRAM2\_PE bit, then before any reading of the unsecure SRAM2 memories (*a* and *b*), initialize them with the CPU1 then start the CPU2. The CPU2 takes care of initializing the SRAM2 secure memories (*a* and *b*).

Note: Unsecure SRAM2 zones that are never read do not require initialization by the CPU1.

# 2.2.23 SRAM2 content lost upon wakeup from Standby if SRAM2\_RST is set

## Description

With the SRAM2\_RST option bit set, the retained SRAM2 content is unduly lost upon wakeup from Standby mode.

*Note:* With the SRAM2\_RST option bit cleared, the retained SRAM2 content is duly kept upon wakeup from Standby mode.

#### Workaround

None.

# 2.2.24 SMPS current surge upon mode change

#### Description

Upon transiting between SMPS *bypass* and SMPS *on* modes, the SMPS may generate a negative current surge (as large as -800 mA) potentially destructive to the device. This occurs with excessive parasitic inductance between the VDDSMPS pin and the decoupling capacitor.

#### Workaround

In the application, place the decoupling capacitor close to the VDDSMPS pin so that the PCB inductance between the decoupling capacitor and the VDDSMPS pin does not exceed **2 nH** for STM32WBx5Cx and STM32WB55Rx, **2.5 nH** for STM32WB55VxQ, and **3 nH** for STM32WB55VxY.

#### 2.2.25 With HSEGMC greater than 3, the HSE accuracy may not fulfill RF requirements

#### Description

HSEGMC[2:0] values above 3 may result in HSE instability that causes a breach of the RF requirements for HSE accuracy.

Keep the value of the HSEGMC[2:0] bitfield lower than 4. That is, keep its bit 2 cleared.

# 2.2.26 Corrupted content of the backup domain due to a missed power-on reset after this domain supply voltage drop

#### Description

The backup domain reset may be missed upon a power-on following a power-off, if its supply voltage drops during the power-off phase hitting a window, which is few mV wide before it starts to rise again. In this critical window, the flip-flops are no longer able to safely retain the information and the backup domain reset has not yet been triggered. This window is located in the range between 100 mV and 700 mV, with the exact position depending mainly on the device and on the temperature.

This missed reset results in unpredictable values of the backup domain registers. This may cause a spurious behavior (such as driving the LSCO output pin on PA2 or influencing backup functions).

#### Workaround

Apply one of the following measures:

- In the application, let the V<sub>DD</sub> and V<sub>BAT</sub> supply voltages fall to a level below 100 mV for more than 200 ms before a new power-on.

- If the above workaround cannot be applied, and the boot follows a power-on reset, erase the backup domain by software.

When the application is using shutdown mode, user needs to discriminate between the power-on reset or an exit from a shutdown mode.

For this purpose, at least one backup register must have been previously programmed with a BKP\_REG\_VAL value with 16 bits set and 16 bits cleared.

Robustness of this workaround can be significantly improved by using a CRC rather than registers. The registers are subject to backup domain reset.

The workaround consists of calculating the CRC of the backup registers: RCC\_BDCR and RTC registers, excluding bits modified by HW.

The CRC result can be stored in the backup register instead of a fixed value. This value needs to be updated for each modification of values covered by CRC, such as by using CRC peripheral. At the very beginning of the boot code, insert the following software sequence:

- 1. Check the BORRSTF flag of the RCC\_CSR register. If set, the reset is caused by a power on, or is exiting from shutdown mode.

- 2. If BORRSTF flag is true, and the shutdown mode is used in the application, check that the backup register value is different from BKP\_REG\_VAL. When tamper detection is enabled, check that no tamper flag is set. If both conditions are met then the reset is caused by a power-on.

- 3. If the reset is caused by a power-on, apply the following sequence:

- a. Enable the PWR clock in the RCC, by setting the PWREN bit.

- b. Enable the backup domain access in the PWR, by setting the DBP bit.

- c. Reset the backup domain, by:

- i. Writing 0x0001 0000 in the RCC\_BDCR register, which sets the BDRST bit and clears other register bits that might not be reset.

- ii. reading the RCC\_BDCR register, to make the reset time long enough

- iii. writing 0x0000 0000 in the RCC\_BDCR register, to clear the BDRST bit

- d. Clear the BORRSTF flag by setting the RMVF bit of the RCC\_CSR register.

# 2.2.27 Overconsumption in Shutdown mode under specific conditions

#### Description

With the PWR\_CR2 register PLS[2:0] bitfield value different from its reset value, the device exhibits an overconsumption of several hundreds of nanoamperes after entering Shutdown mode.

Before entering Shutdown mode while PLS[2:0] is not at its reset value, set PLS[2:0] to its reset value and wait for at least the time specified in the following table.

| τ. (%C)             | Minimum waiting time (μs) |                        |                          |                          |  |  |

|---------------------|---------------------------|------------------------|--------------------------|--------------------------|--|--|

| Т <sub>Ј</sub> (°С) | V <sub>DDA</sub> = 2 V    | V <sub>DDA</sub> = 3 V | V <sub>DDA</sub> = 3.3 V | V <sub>DDA</sub> = 3.6 V |  |  |

| -40                 | 26                        | 38                     | 42                       | 45                       |  |  |

| 25                  | 20                        | 29                     | 32                       | 35                       |  |  |

| 50                  | 18                        | 27                     | 29                       | 32                       |  |  |

| 105                 | 15                        | 23                     | 25                       | 27                       |  |  |

# 2.2.28 Excessive current on V<sub>DDA</sub> or V<sub>DD</sub> when V<sub>DD</sub> level is different from V<sub>DDA</sub> level

# Description

When  $V_{DDA}$  level is different from  $V_{DD}$  level, excessive current is present on  $V_{DDA}$  or  $V_{DD}$ .

Note: Packages other than UFQFPN48 packages are not affected by this limitation.

## Workaround

Maintain the  $V_{DDA}$  level equal to  $V_{DD}$  level.

Refer to the following electrical characteristics, specific to UFQFPN48 packages.

#### Table 5. General operating conditions

| Symbol           | Parameter             | Parameter Conditions Min                   |                                     | Мах                               | Unit |

|------------------|-----------------------|--------------------------------------------|-------------------------------------|-----------------------------------|------|

| V <sub>DDA</sub> |                       | ADC or COMP used                           | V <sub>DD</sub> -50 mV              | min (V <sub>DD</sub> +50 mV, 3.6) |      |

|                  | Analog supply voltage | VREFBUF used                               | max (V <sub>DD</sub> -50 mV, 2.35)  | min (V <sub>DD</sub> +50 mV, 3.6) | V    |

|                  |                       | ADC, COMP, VREFBUF not used <sup>(1)</sup> | max (V <sub>DD</sub> - 50 mV, 1.71) | min (V <sub>DD</sub> +50 mV, 3.6) |      |

1. When not used,  $V_{DDA}$  must be connected to  $V_{DD}$ .

#### Table 6. Absolute maximum ratings

| Symbol Ratings              | Voltage characteristics                                            |     |     |      |

|-----------------------------|--------------------------------------------------------------------|-----|-----|------|

| Symbol                      | raunys                                                             | Min | Max | Unit |

| $ \Delta (V_{DD} V_{DDA}) $ | Difference between $V_{\text{DD}}$ and $V_{\text{DDA}}$ power pins |     | 0.3 | V    |

# 2.3 Radio system

# 2.3.1 RF system wake-up clock set to HSE/1024 cannot be changed

#### Description

Once the RFWKPSEL[1:0] bitfield of the RCC\_CSR register is set to 11, setting it to any other value or performing a system reset prevents the RF system from waking with another wakeup clock.

Note: The value 11 of the bitfield selects HSE divided by 1024 as the RF system wakeup clock.

## Workaround

Apply a POR to change the RF system wakeup clock.

# 2.4 DMA

# 2.4.1 DMA disable failure and error flag omission upon simultaneous transfer error and global flag clear

# Description

Upon a data transfer error in a DMA channel x, both the specific TEIFx and the global GIFx flags are raised and the channel x is normally automatically disabled. However, if in the same clock cycle the software clears the GIFx flag (by setting the CGIFx bit of the DMA\_IFCR register), the automatic channel disable fails and the TEIFx flag is not raised.

This issue does not occur with ST's HAL software that does not use and clear the GIFx flag when the channel is active.

#### Workaround

Do not clear GIFx flags when the channel is active. Instead, use HTIFx, TCIFx, and TEIFx specific event flags and their corresponding clear bits.

# 2.5 DMAMUX

# 2.5.1 SOFx not asserted when writing into DMAMUX\_CFR register

#### Description

The SOFx flag of the DMAMUX\_CSR status register is not asserted if overrun from another DMAMUX channel occurs when the software writes into the DMAMUX\_CFR register.

This can happen when multiple DMA channels operate in synchronization mode, and when overrun can occur from more than one channel. As the SOFx flag clear requires a write into the DMAMUX\_CFR register (to set the corresponding CSOFx bit), overrun occurring from another DMAMUX channel operating during that write operation fails to raise its corresponding SOFx flag.

#### Workaround

None. Avoid the use of synchronization mode for concurrent DMAMUX channels, if at least two of them potentially generate synchronization overrun.

# 2.5.2 OFx not asserted for trigger event coinciding with last DMAMUX request

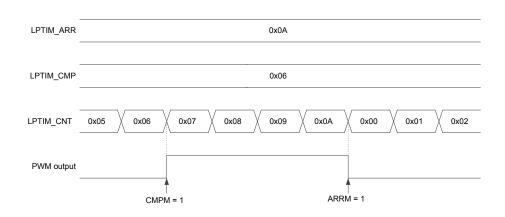

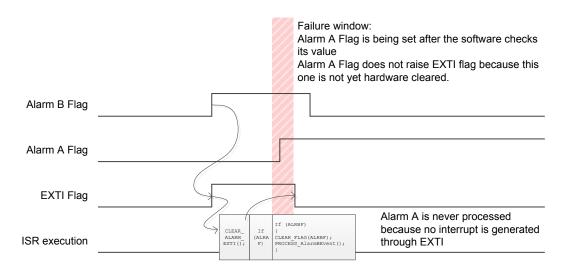

#### Description